This is the accepted manuscript made available via CHORUS. The article has been published as:

# Implementing Boolean Functions in Hybrid Digital-Analog Systems

Vivek Kohar, Behnam Kia, John F. Lindner, and William L. Ditto Phys. Rev. Applied **7**, 044006 — Published 11 April 2017

DOI: 10.1103/PhysRevApplied.7.044006

# Implementing Boolean functions in hybrid digital-analog systems

Vivek Kohar, <sup>1,\*</sup> Behnam Kia, <sup>1</sup> John F. Lindner, <sup>2</sup> and William L. Ditto <sup>1</sup> Dept. of Physics, North Carolina State University, Raleigh, NC 27695-8202, USA <sup>2</sup> Physics Department, The College of Wooster, Wooster, OH 44691, USA (Dated: February 27, 2017)

We propose an architecture to implement multi-input one-output Boolean functions using chaos computing in hybrid digital-analog systems consisting of a digital block of conventional AND gates and a nonlinear circuit. This architecture efficiently utilizes the super-stable initial conditions of a nonlinear circuit and enables us to implement all possible  $2^{2^m}$  Boolean functions of m data inputs in just m iterations of the nonlinear circuit resulting in better operating speed and noise tolerance. In an ideal nonlinear map, this architecture eliminates the need for a decoder as the outputs are mapped to maxima and minima of the map and can be fed directly to the next stage enabling multilayer concatenation. We demonstrate the utility of this architecture in a 3-transistor circuit.

#### I. INTRODUCTION

The impending failure of Moore's law has led to the development of novel approaches like nonlinear or chaos computing (CC) [1-4] to get more computation out of a limited number of transistors. It was shown recently that a simple nonlinear circuit can theoretically implement an infinite number of functions [5] which in practice are limited by amplification of ambient noise with each iteration. Researchers have described an integrated circuit implementation of CC with a nonlinear circuit [6] as well as other transistor-based implementations of chaotic circuits [7, 8]. CC allows us to get different multi-input one-output functions using the same hardware giving us a reconfigurable logic block. We can change the functionality of the logic block by changing the control signals and get any function that we need. Moreover, this hardware is fully compatible with conventional digital systems and can be fabricated on integrated circuits using the same semiconductor fabrication technologies.

Manufacturing nonidealities and ambient noise limit the number of functions that we can obtain from these nonlinear circuits in practice. The ambient noise is amplified exponentially when the circuits are operating in the chaotic regime thereby limiting the number of iterations for which we can use the nonlinear circuit. The number of implementable functions increases exponentially with the number of iterations [5], so it is crucial that we can maximize the iterations for which output can be obtained successfully. One method to achieve this objective is to suppress the noise evolution through coupled redundant nonlinear circuits as the local noise in different circuits averages out and the overall deviation in the output is reduced [9–11].

In this article, we propose an alternate method which exponentially decreases the number of iterations required to implement all Boolean functions. This method utilizes a hybrid digital-analog system consisting of conventional digital circuits and an analog nonlinear circuit and distributes the computation between the digital and nonlinear circuit. The increase in hardware complexity due to digital block is compensated to a large extent by a corresponding reduction in the complexity of the encoder. Hybrid digital-analog systems have been proposed as emerging technologies for transmission [12, 13], wireless video coding [14], control systems [15], and chaotic circuits [16].

#### II. THEORETICAL FRAMEWORK

Let us assume that both data, as well as control signals, are Boolean variables and we want to implement all Boolean functions  $f: B^m \to B$ , where  $B = \{0, 1\}$  of m data inputs. The m Boolean data inputs,  $d_1, d_2...d_m$ result in  $2^m$  distinct input combinations as each input can take two values, namely, 0 and 1. The output corresponding to these input combinations can be 0 or 1 and consequently, the number of all possible multi-input one—output Boolean functions for m data inputs is  $2^{2^m}$ . For example, two data inputs  $d_1$  and  $d_2$  result in  $2^2$  different input combinations 00, 01,10 and 11 and  $2^{2^2} = 16$ distinct functions corresponding to an output of 0 or 1 for these 4 input combinations. For a CC element to yield all possible Boolean functions, we need 16 different control signals to select a specific function to be implemented. These control signals can be provided by 4 control inputs  $c_1, c_2, c_3,$  and  $c_4$ . In other words, we need control signals  $c_1, c_2, \ldots, c_{2^m}$  to implement all m-input 1-output functions.

CC is a paradigm to utilize the nonlinearity of physical systems to obtain Boolean functions [4, 17]. The primary advantage of CC elements is their reconfigurability, which allows extraction of different Boolean functions from the same hardware. Control signals are used to select a specific Boolean function to be implemented. In the conventional CC approach, an encoder takes the digital data inputs and control signals as input and generates an analog output that is transformed to an initial condition of a nonlinear circuit. The nonlinear circuit initialized with this value is iterated for a fixed number of

<sup>\*</sup> vkohar@ncsu.edu

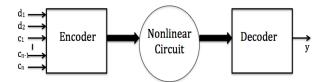

FIG. 1. Schematic diagram of conventional nonlinear or chaos computing.

iterations and the output is then fed to a decoder which transforms it to a digital output as shown in Fig. 1.

One can employ different encoding schemes to convert data inputs and control signals to an analog value. A simple example is digital-to-analog converter (DAC) for which the encoding can be expressed as

$$x_e = \frac{2^n d_1 + \dots + 2^{n-m-1} d_m + 2^{n-m} c_1 + \dots + 2^0 c_{n-m}}{2^{n+1}},$$

(1)

where n is equal to the sum of the number of data inputs and control signals. Every possible combination of data inputs and control signals is mapped to a distinct analog value yielding a total of distinct  $2^n$  analog values. The nonlinear circuit is initialized with an initial condition  $x_0$  given by

$$x_0 = g(x_e), (2)$$

where g(x) is typically a scaling function and depends on the characteristics of the nonlinear circuit. For example, if the nonlinear circuits consists of transistors with input voltages in [0V, 5V], then  $x_0 = g(x_e) = 5x_e$ . Similarly the decoder is typically a thresholding circuit such that the output y of the decoder can be given as

$$y = D[x_T] = \begin{cases} 0 & x_T \le \tau \\ 1 & x_T > \tau, \end{cases}$$

(3)

where  $\tau$  is threshold, and T is the number of iterations of the nonlinear circuit.

The number of functions that can be obtained depends on the computing exponent [5] of the nonlinear circuit, and the maximum number of functions can be obtained in the chaotic region. The actual number of functions that we obtain is less than  $2^{2^m}$  as some of the control functions yield the same function even in the chaotic region [5] and all possible functions can be obtained only if  $n \gg 2^m$ . Moreover, a large number of iterations are needed to obtain these functions. For example, for 4 inputs bits and 16 control signals, we get about 16 distinct functions after 6 iterations and 56 functions after 10 iterations [5]. This number saturates at about 22000 after 30 iterations which are about one—third of all possible functions (65536). Ambient noise and finite resolution of experimental devices severely restricts the maximum number of iterations. For example, the reliability of a recently fabricated nonlinear circuit [6] starts decreasing from sixth iteration onwards. Thus it is imperative to

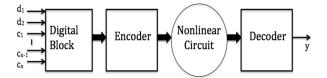

FIG. 2. Schematic diagram of chaos computing in hybrid digital-analog systems.

devise an approach that can fully utilize the potential of the nonlinear circuit and yield maximum functions in minimum number of iterations.

We propose the hybrid architecture shown in Fig. 2. It optimally utilizes the potential of chaos computing as it can theoretically implement all Boolean functions with minimum number of control signals. In this architecture, the data inputs and control signals are first passed through a digital block to generate all possible combinations of data inputs and then each combination is associated with a control signal (see Appendix). The number of combinations of data inputs can be found using the binomial coefficients  $C_k^m$ , which denote the possible number of combinations of m data inputs considered k at a time. From the properties of binomial coefficients we know that  $\sum_{k=0}^{m} C_k^m = 2^m$ , and hence the number of control signals that we need agrees with the number we had found previously.

The underlying principle behind this architecture is that various Boolean functions can be expressed as logical functions of combinations of data inputs and the control signals determine if a specific combination contributes to the output of a function or not. The analog circuit including the nonlinear circuit determines whether the selected combinations should be mapped to 0 or 1. In this architecture, the encoder is an averaging circuit which is much simpler than a DAC as needed in the conventional architecture and compensates for the increased hardware necessity of the digital block. The encoded analog value  $x_e$  of the encoder can be given as

$$x_e = \frac{\sum\limits_{i=1}^{2^m} c_i \wedge X_i}{2^m}.$$

(4)

For example, for 2-data inputs, we have

$$x_e = \frac{c_1 + c_2 \wedge d_1 + c_3 \wedge d_2 + c_4 \wedge d_1 \wedge d_2}{2^2}.$$

(5)

Note that the encoder in this scheme produces only  $2^m+1$  encoded values as opposed to  $2^{2^m}$  encoded values needed in Eq. 1. In other words, the number of initial conditions that are to be resolved decreases exponentially in this hybrid architecture. The number of distinct functions to which an encoded value contributes is simply the binomial coefficient corresponding to that encoded value i.e.  $C_k^{2^m}$  for  $0 \le k \le 2^m$ . The sum of these coefficients will be  $2^{2^m}$  which is equal to the maximum number of Boolean functions for m data inputs.

In this architecture, each encoded value  $x_e$  is mapped to a super-stable initial condition of the nonlinear circuit and the functional form of g(x) depends on the nonlinear circuit. For a generic map,  $x_i = f(x_{i-1})$ , the super-stable initial conditions for iteration i are the initial conditions,  $x_0$ , for which  $\frac{d}{dx}f^i(x_0) = 0$  or  $f^i(x_0)$  is a maxima or minima of  $f^i(x)$ . Using Taylor's expansion for an initial condition  $(x_0 + \delta)$  representing a small perturbation  $\delta$ , of the initial condition  $x_0$ , we can approximate the  $i^{th}$ iteration for  $x_0 + \delta$  by  $f^i(x_0) + \delta \frac{d}{dx}(f^i(x_0))$  after neglecting second and higher order terms. If  $\frac{d}{dx}(f^i(x_0)) = 0$ , then the second term will be zero and the difference between  $f^i(x_0)$  and  $f^i(x_0 + \delta)$  is proportional to higher order terms which are very close to zero if  $\delta$  is small. So, the super-stable initial conditions of the nonlinear circuit are robust against perturbations [11] and map to maxima and minima of the response function of the nonlinear circuit.

If the nonlinear circuit is piecewise linear with the same domain and codomain like a Tent map, then g(x) is simply a scaling function as in Eq. 2. For higher-order nonlinearity, g(x) is a nonlinear function as the superstable initial conditions are non-uniformly distributed. The nonlinear circuit maps the neighboring super-stable initial conditions to different output values. If the domain and codomain of the response function of the nonlinear circuit are same, then, the maxima and minima correspond to 0 and 1 respectively, and a decoder is not needed. If domain and codomain are different, then a decoder is needed, which can be same as the conventional CC decoder given in Eq. 3.

TABLE I. Comparison of conventional and hybrid digitalanalog chaos computing

| Feature                  | Conventional       | Hybrid dgital-analog           |

|--------------------------|--------------------|--------------------------------|

| Digital block<br>Encoder | Not needed<br>DAC  | AND gates<br>Averaging Circuit |

| Minimum Iterations       | $2^m$              | m                              |

| Decoder                  | Threshold detector | Not needed                     |

| Noise Tolerance          | Less               | More                           |

A comparison of conventional and hybrid architectures for chaos computing is shown in Table. I. Digital block in the hybrid digital-analog architecture adds to the complexity of the circuit but the overall complexity of this approach is lower or comparable to the conventional approach. In the conventional approach, the encoder is a  $(m+2^m)$  bit digital-to-analog converter whereas a  $(2^m+1)$  bit averaging circuit is used as an encoder in the hybrid approach. The VLSI implementation of hybrid CC encoder is simpler and occupies less space and compensates for the additional digital block hardware. Elimination of decoder further reduces the space complexity of the hybrid approach. Hybrid approach is better

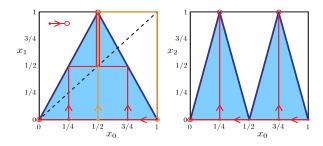

FIG. 3. Output of the Tent map after one  $(x_1)$  iteration and two iterations  $(x_2)$ . Mapping of super-stable initial conditions  $x_0$  to  $x_2$  is shown by arrows.

in terms of time complexity also as the time complexity of nonlinear circuit is much lower and compensates for the increased time complexity due to the digital block.

#### III. EXPLICIT EXAMPLE

Now we illustrate the hybrid architecture through the 2—data input example. Let us assume that the nonlinear circuit is the Tent map given by,

$$x_{i+1} = f_{\mu}(x_i) = \begin{cases} \mu x_i & \text{for } x_i < \frac{1}{2} \\ \mu(1 - x_i) & \text{for } \frac{1}{2} \le x_i. \end{cases}$$

(6)

which is chaotic for  $\mu=2$  and maps an initial condition  $x_0\in[0,1]$  to  $x_{i+1}\in[0,1]$ . The super-stable initial conditions for first iteration are  $x_0=0,0.5,1$ , which map to 0,1,0 respectively. At the next iteration, the maxima at 0.5 changes to minima and two new maxima appear at 0.25 and 0.75 as shown in Fig. 3. One can find super-stable initial conditions at any iteration i by finding the roots of the equation  $\frac{d}{dx}(f^i(x))=0$ . At any iteration i, there will be  $2^{i-1}$  copies of the Tent and the super-stable initial conditions corresponding to maxima and minima will be  $0,1/2^i,2/2^i,3/2^i\dots(2^i-1)/2^i,1$ . There are  $2^{i-1}$  maxima and  $2^{i-1}+1$  minima for a total of  $2^i+1$  super-stable points. This gives us a one to one correspondence between the number of data inputs m, and the iterations i, required to obtain all possible functions for those data inputs.

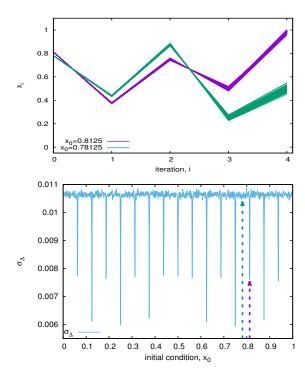

To study the noise robustness of different initial conditions, we add noise terms to  $x_0$  as well as at every subsequent iterate  $x_j$  for  $1 \le j \le i$  such that the noisy map can be written as  $x_i = f(x_{i-1} + \delta_{i-1})$  where  $\delta_{i-1}$  is the instantaneous noise term with zero mean and standard deviation  $\sigma$ . One hundred trajectories of the Tent map for two different initial conditions are shown in Fig. 4 and we observe that divergence of the super-stable initial condition  $x_0 = 0.8125$  is much lower compared to divergence of trajectories starting with  $x_0 = 0.78125$ . We calculate the deviation  $\Delta$  as the deviation of the noisy trajectory from the noiseless trajectory and plot the standard deviation  $\sigma_{\Delta}$  of these deviations in Fig. 4. We observe that

FIG. 4. (Color online) Iterations of two nearby initial conditions of Tent map in presence of ambient Gaussian noise of zero mean and standard deviation  $\sigma = 10^{-3}$ . One hundred trajectories are shown for each initial condition.  $x_0 = 0.8125$  is a super-stable initial condition for i = 4 and consequently the trajectories stay close to each other in comparison to a non super-stable initial condition,  $x_0 = 0.78125$ . The standard deviation  $\sigma_{\Delta}$  of deviation  $\Delta$  of  $10^4$  noisy trajectories from a noiseless trajectory for initial conditions  $\in [0, 1]$  after 4 iterations of the Tent map is shown in the bottom panel. The initial conditions used in the top panel are marked by arrows.

the  $\sigma_{\Delta}$  of super-stable initial conditions is significantly less compared to  $\sigma_{\Delta}$  of nearby initial conditions.

The data inputs and control signals are encoded and mapped to initial conditions according to Eq. 5 and Eq. 2 such that g(x) = x. The encoded values or the corresponding initial conditions of the Tent map are shared by different combinations of data inputs and control signals as sixteen possible combinations have been mapped to just five distinct initial conditions. The output of the Tent map after two iterations for  $x_0 \in [0,1]$  is shown in Fig. 3. Note that we do not need a decoder in this case and the outputs corresponding to different control and data bits are given in Table. II. In summary, we observe that all the sixteen different functions for 2 data inputs can be implemented by using 4 control signals and five initial conditions of the Tent map which are resolved in just two iterations.

TABLE II. Truth tables and instruction sets.

| Control bits     |      | $[d_1d_2]$ |      |      | Function |

|------------------|------|------------|------|------|----------|

| $[c_1c_2c_3c_4]$ | [00] | [01]       | [10] | [11] |          |

| 0000             | 0    | 0          | 0    | 0    | 0        |

| 0001             | 0    | 0          | 0    | 1    | 1        |

| 0010             | 0    | 1          | 0    | 1    | 2        |

| 0011             | 0    | 1          | 0    | 0    | 3        |

| 0100             | 0    | 0          | 1    | 1    | 4        |

| 0101             | 0    | 0          | 1    | 0    | 5        |

| 0110             | 0    | 1          | 1    | 0    | 6        |

| 0111             | 0    | 1          | 1    | 1    | 7        |

| 1000             | 1    | 1          | 1    | 1    | 8        |

| 1001             | 1    | 1          | 1    | 0    | 9        |

| 1010             | 1    | 0          | 1    | 0    | 10       |

| 1011             | 1    | 0          | 1    | 1    | 11       |

| 1100             | 1    | 1          | 0    | 0    | 12       |

| 1101             | 1    | 1          | 0    | 1    | 13       |

| 1110             | 1    | 0          | 0    | 1    | 14       |

| 1111             | 1    | 0          | 0    | 0    | 15       |

#### IV. PRACTICAL APPLICATION

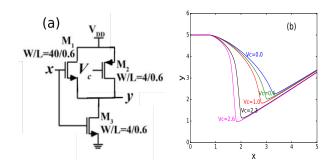

In this section, we demonstrate the implementation of multi-input one-output functions using a three transistor nonlinear circuit shown in Fig. 5(a). This nonlinear circuit is implemented in Cadence Spectre using the ONC5,  $0.5 - \mu m$  process models provided by the vendor. The output from Cadence simulator is fed back as its input to generate further iterations. For practical considerations, we limit the accuracy in feedback process to  $10\mu V$ . Further implementation details are available in Ref. [5, 6]. This simple circuit exhibits different behaviors depending on the bias voltage  $V_c$  which acts as a bifurcation parameter (see Fig. 8). The response y, of the circuit for various input voltages x, at different bifurcation voltages  $V_c$ , is shown in Fig. 5(b).

FIG. 5. (Color online) (a) A three transistor nonlinear circuit. (b) Nonlinear response curve of the circuit for different  $V_c=0,0.6,1.0,2.3,2.6V$ .

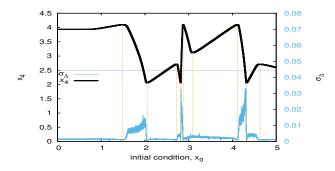

FIG. 6. (Color online) Fourth iteration of the map for  $V_c = 0.5V$  and the standard deviation  $\sigma_{\Delta}$  of the deviations of a noisy map from that of a noiseless map are also shown. The noise is assumed to be Gaussian with zero mean and 0.001 standard deviation. Number of functions which can be implemented using the hybrid architecture.

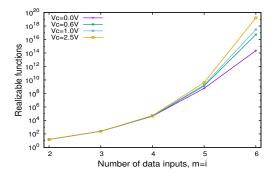

FIG. 7. (Color online) The iteration number i, after which we calculate the implementable functions is taken to be equal to the number of data inputs m. Note the exponential increase in the number of implementable functions on a log scale indicating that the increase in the number of functions is proportional to  $2^{2^m} = 2^{2^i}$ .

Conventional CC can be implemented in this circuit by using a DAC as encoder which encodes the data inputs and control signals to an analog value according to Eq. 1 and the scaling these values to [0V, 5V]. If we consider the case of 2-data inputs and 4-control signals and use a 6-bit DAC as encoder, we get 64 analog values. For each control signal, there are 4 different analog values and each analog value corresponds to a unique combination of data inputs and control signals. Let us suppose that we iterate the map four times. The fourth iterate of the map for  $V_c = 0.5V$  is shown in Fig. 6. The function implemented by a control signal can be found out by finding the output for all four analog values corresponding to that control signal. For example, the control signal 0000 results in four analog values 0, 1.25, 2.5, 3.75V which are mapped to 3.94, 4.04, 2.51, 3.76V or a decoded output of 1111 that corresponds to function number 8 as per Table. II. Similarly, the control signal 0001 will implement function 8. We find that even after 4 iterations, nearby initial conditions are not resolved by the map and we can implement few functions only[5].

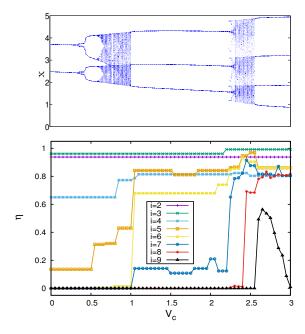

FIG. 8. (Color online) The ratio  $(\eta)$  of implementable functions versus the maximum number of possible functions plotted for different values of bifurcation parameter  $V_c$  and the number of iterations i (data inputs, m). The bifurcation diagram of the nonlinear circuit for corresponding  $V_c$  values is shown at the top.

To implement CC using the hybrid architecture, we pass the digital data inputs and control signals to a digital simulator and the output of the digital block is then passed through an encoder which encodes them according to Eq. 4. From Fig. 5, we observe that this nonlinear circuit maps the input values in [0V, 5V] to a smaller range that depends on the bias voltage  $V_c$  or, in other words, the domain and codomain for this nonlinear circuit are different. We can either limit the input range to keep domain and codomain same or perform a nonlinear transformation of the encoded value to map  $x_e$ to super-stable initial conditions of the nonlinear circuit. We follow this second approach of nonlinear transformation and calculate the number of functions that can be implemented with m data inputs after m iterations at different bias values.

The initial conditions where the map in Fig. 6 takes a minimum or maximum value are marked by vertical lines and one can observe that the standard deviation of the deviations of the noisy map from noiseless map is typically low for these initial conditions as compared to nearby initial conditions. Due to the asymmetry of the response of the nonlinear circuit, the number of superstable points is sometimes less than  $2^m + 1$ . For example, in Fig. 6 there are 9 super-stable initial conditions between (0V, 5V). Including 0V and 5V provides us a total of 11 initial conditions that can be used to map 11 encoded values which is less than  $2^i + 1 = 17$  for i = 4. In such cases, we assume that the functions which encode

the data inputs and control signals to larger encoded values cannot be implemented. The number of functions corresponding to  $j^{th}$  encoded value  $x_e$  is equal to  $C_j^{2^m}$ . In the specific example, only the functions that encode all their data inputs and control signals to first 11 values can be implemented. If we want to implement all the functions then we need to iterate the map for more iterations so that the number of super-stable initial conditions is equal to or more than  $2^m + 1$ .

As the domain and codomain are different, we will need a decoder in this case. We fix the decoder threshold at  $\tau = 2.5V$ , so that an output from the nonlinear circuit after m iterations is taken as logic 1 only if it is greater than 2.5V and 0 otherwise. Thus nearby super-stable initial conditions representing local minima and maxima of the nonlinear circuit are mapped to 0 and 1 by the decoder. If the maxima remains below 2.5V or minima is above 2.5V, we take that as an error and the functions corresponding to such encoded value  $x_e$  are counted as non-implementable. For example, for the  $4^{th}$  iteration of the circuit for  $V_c = 0.5V$ , the minima at 0V, 3.09V, 5V are all above 2.5V and result in an error. Thus the total number of non-implementable functions is obtained by adding the number of functions corresponding to encoded values which cannot be mapped to an initial condition due to less number of super-stable initial conditions as discussed in the previous paragraph and the encoded values which are mapped to initial conditions corresponding to maxima below the decoder threshold or minima above the decoder threshold.

The number of implementable functions for different number of data inputs is shown in Fig. 7. We observe that the number of implementable functions increases very rapidly with the number of iterations or data inputs as the map is iterated m times for m data inputs. If we iterate more than m times, then the number of implementable functions will be equal to the minimum of implementable functions for that iteration and the number of all possible functions,  $2^{2^m}$ .

Next, we calculate the ratio  $\eta$ , of the number of implementable functions using this nonlinear circuit to all possible functions  $2^{2^m}$ . We start with m data inputs,  $2^m$  control signals and iterate the nonlinear circuit for m iterations. The results for different m and bifurcation parameter,  $V_c$  are shown in Fig. 8. We observe that the  $\eta$  increases near chaotic regions of the nonlinear circuit as the nonlinear circuit undergoes bifurcations. The number of implementable functions stays high in the period-3 window as the basin of attraction of different fixed points is riddled. Changes in  $V_c$  also affect the maxima and minima and occasionally the number of implementable functions decreases as the maxima falls below  $\tau$  or minima is above  $\tau$ . Further, the domain and codomain are different for this nonlinear circuit, the effect of bifurcation parameter is subdued by a decrease in the number of super-stable initial conditions. These results suggest that a small digital block in our hybrid architecture can enable exponential increase in the number of functions that

can be implemented for a particular iteration number of the nonlinear circuit.

#### V. CONCLUSION

We have proposed an architecture to implement multiinput one-output Boolean functions in a hybrid digitalanalog circuit. The digital block consists of AND gates to generate  $2^m$  combinations of m data inputs and associate each combination with a control signal. The output of the digital block is used as an input to an encoder which maps it to  $2^m + 1$  analog values which are used to initialize the nonlinear circuit with corresponding super-stable initial conditions. The nonlinear circuit resolves the initial conditions such that alternate initial conditions are mapped to maxima and minima of the map after m iterations. The output is then decoded using a simple threshold detecting decoder. This architecture is robust to noise as the effect of noise is minimum at super-stable initial conditions and can scale superlinearly by coupling redundant circuits [11]. Moreover, if the domain and codomain of the nonlinear circuit are same, then the output can be used directly as an input to the next stage, allowing an easy concatenation of CC elements. We have also demonstrated the utility of this architecture in a 3-transistor nonlinear circuit. Transistor based nonlinear circuits and digital blocks can be built on the same integrated circuit [6] and this hybrid architecture makes it possible to implement a large number of functions as the output can be obtained in few iterations of the nonlinear circuit and the smearing of output due to exponential amplification of noise can be avoided.

### VI. ACKNOWLEDGMENTS

We gratefully acknowledge support from North Carolina State University (NCSU) Grant 201584-70677 and the Office of Naval Research under STTR grant No. N00014-14-C-0033.

## VII. APPENDIX

Here the combinations imply the logical AND  $(\land)$  of the k data inputs. For example, we have  $C_0^m$  or 1 combination when no input data is selected,  $C_1^m$  or m combinations when a single data input is selected,  $C_2^m$  combinations when 2 data inputs are selected  $(d_i \land d_j$  for  $1 \leq i < m$  and  $i < j \leq m)$  and  $C_m^m$  or 1 combination  $(d_1 \land d_2 \land \ldots d_m)$  consisting of all the data inputs. We need  $C_2^m + C_3^m + \cdots + C_m^m$ 2—input AND gates to generated these combinations as we can use output of k-1 data input combination and generate a k input data combination by its logical AND with another data input. Let us denote these combinations of data

inputs by  $X_i$  for  $1 \leq i \leq 2^m$ . Each of these combinations  $X_i$  is then associated with a control signal  $c_i$  through an additional logical AND operation. The association with control signals will require a further  $(2^m-1)$

2—input AND gates as no gate is required for the first control signal. Thus the digital block requires about  $(2^m - C_0^m - C_1^m) + (2^m - 1) = (2^{m+1} - m - 2)$  2—input AND gates.

- Julien Borghetti, Zhiyong Li, Joseph Straznicky, Xuema Li, Douglas AA Ohlberg, Wei Wu, Duncan R Stewart, and R Stanley Williams, "A hybrid nanomemristor/transistor logic circuit capable of self-programming," Proceedings of the National Academy of Sciences 106, 1699–1703 (2009).

- [2] Fangyue Chen, Guolong He, and Guanrong Chen, "Realization of boolean functions via cnn: Mathematical theory, lsbf and template design," IEEE Transactions on Circuits and Systems I: Regular Papers **53**, 2203–2213 (2006).

- [3] Fangyue Chen, Guanrong Chen, Qinbin He, Guolong He, and Xiubin Xu, "Universal perceptron and dna-like learning algorithm for binary neural networks: non-lsbf implementation," IEEE Transactions on Neural Networks 20, 1293–1301 (2009).

- [4] Sudeshna Sinha and William L. Ditto, "Dynamics based computation," Phys. Rev. Lett. 81, 2156–2159 (1998).

- [5] B. Kia, J. F. Lindner, and W. L. Ditto, "A simple non-linear circuit contains an infinite number of functions," IEEE Transactions on Circuits and Systems II: Express Briefs 63, 944–948 (2016).

- [6] B. Kia, K. Mobley, and W. L. Ditto, "An integrated circuit design for a dynamics-based reconfigurable logic block," IEEE Transactions on Circuits and Systems II: Express Briefs PP, 1–5 (2016).

- [7] Lars Keuninckx, Guy Van der Sande, and Jan Danckaert, "Simple two-transistor single-supply resistor capacitor chaotic oscillator," IEEE Transactions on Circuits and Systems II: Express Briefs 62, 891–895 (2015).

- [8] Chunbiao Li, Julien Clinton Sprott, Wesley Thio, and Huanqiang Zhu, "A new piecewise linear hyperchaotic circuit," IEEE Transactions on Circuits and Systems II: Express Briefs 61, 977–981 (2014).

- [9] Vivek Kohar, Behnam Kia, John F Lindner, and William L Ditto, "Reduction of additive colored noise

- using coupled dynamics," International Journal of Bifurcation and Chaos **26**, 1650005 (2016).

- [10] Vivek Kohar, Sarvenaz Kia, Behnam Kia, John F Lindner, and William L Ditto, "Role of network topology in noise reduction using coupled dynamics," Nonlinear Dynamics 84, 1805–1812 (2016).

- [11] Vivek Kohar, Behnam Kia, John F Lindner, and William L Ditto, "Superlinearly scalable noise robustness of redundant coupled dynamical systems," Physical Review E **93**, 032213 (2016).

- [12] Matthias Rüngeler, Johannes Bunte, and Peter Vary, "Design and evaluation of hybrid digital-analog transmission outperforming purely digital concepts," IEEE Transactions on Communications 62, 3983–3996 (2014).

- [13] Vinod M Prabhakaran, Rohit Puri, and Kannan Ramchandran, "Hybrid digital-analog codes for sourcechannel broadcast of gaussian sources over gaussian channels," IEEE Transactions on Information Theory 57, 4573–4588 (2011).

- [14] Lei Yu, Houqiang Li, and Weiping Li, "Wireless scalable video coding using a hybrid digital-analog scheme," IEEE Transactions on Circuits and Systems for Video Technology 24, 331–345 (2014).

- [15] Rafal Goebel, Ricardo G Sanfelice, and Andrew R Teel, "Hybrid dynamical systems," IEEE Control Systems 29, 28–93 (2009).

- [16] Jonathan N. Blakely, Roy M. Cooper, and Ned J. Corron, "Regularly timed events amid chaos," Phys. Rev. E 92, 052904 (2015).

- [17] William L Ditto and Sudeshna Sinha, "Exploiting chaos for applications," Chaos: An Interdisciplinary Journal of Nonlinear Science 25, 097615 (2015).