This is the accepted manuscript made available via CHORUS. The article has been published as:

# Device Isolation in Hybrid Field-Effect Transistors by Semiconductor Micropatterning Using Picosecond Lasers

Robert M. Ireland, Yu Liu, Josef W. Spalenka, Supriya Jaiswal, Kenshi Fukumitsu, Shingo Oishi, Hiroshi Saito, Mochizuki Ryosuke, Paul G. Evans, and Howard E. Katz Phys. Rev. Applied **2**, 044006 — Published 15 October 2014

DOI: 10.1103/PhysRevApplied.2.044006

# Device isolation in hybrid field-effect transistors by semiconductor micropatterning using picosecond lasers

Robert M. Ireland, Yu Liu, Josef Spalenka, Supriya Jaiswal, Kenshi Fukumitsu, Shingo Oishi, Hiroshi Saito, Mochizuki Ryosuke, Paul Evans\*, and Howard E. Katz\*

[\*] Prof. Howard E. Katz, Robert M. Ireland, Yu Liu Department of Materials Science and Engineering and Department of Chemistry, Johns Hopkins University, 3400 North Charles Street, Baltimore, MD

Supriya Jaiswal, Hamamatsu Corporation, 360 Foothill Road, Box 6910. Bridgewater, NJ 08807-0910

Kenshi Fukumitsu, Shingo Oishi, Hiroshi Saito, Mochizuki Ryosuke, Hamamatsu Photonics K.K, 5000, Hirakuchi, Hamakita-ku, Hamamatsu City, Shizuoka Pref., 434-8601Japan. http://www.hamamatsu.com

[\*] Prof. Paul G. Evans, Josef W. Spalenka, Department of Materials Science and Engineering, University of Wisconsin, Madison, WI 53706

E-mail: hekatz@jhu.edu; evans@engr.wisc.edu

Receipt date:

A solid-state picosecond laser is used to ablate semiconductor thin films in spatially localized areas, providing an alternative to device isolation strategies based on chemical or ion etching techniques. Field-effect transistors (FET) of emerging organic and inorganic materials often utilize continuous semiconductor film and an array of top-contact electrodes. Electrically isolating individual FET components from other circuit elements is essential in order to reduce parasitic capacitances and unwanted current pathways, in order both to improve device performance and to enable the observation of new or enhanced physical phenomena. We pattern FET arrays with ultrafast pulse duration (1.5 ps) and low fluence (0.09 J cm<sup>-2</sup>) optical pulses using the fundamental wavelength (1030 nm) of an Yb-YAG laser. We investigate two representative semiconductor materials. First, zinc oxide (ZnO) is deposited onto Si/SiO<sub>2</sub> substrates by sol-gel methods and used to create n-channel FETs with aluminum top electrodes. Isolation of individual FETs enables the clear observation of photomodulation of the FET device parameters via photoinduced electron donation from an adsorbed chromophore. The second system comprises thin-film bilayers of tellurium and organic semiconductor molecules sequentially vapor-deposited onto Si/SiO<sub>2</sub> substrates, with gold electrodes deposited last. Charge carrier mobility is maintained for devices isolated by picosecond lasers, but leakage currents through the FET dielectric are drastically reduced.

Keywords: zinc oxide, tellurium, organic semiconductor, field-effect transistor, leakage current, picosecond laser

### I. INTRODUCTION

Thin-film electronic technology based on organic and inorganic semiconductors has seen improvements in performance and processing during recent years, motivated by low-cost and large-area fabrication of chemical sensors, active-matrix displays, and transparent or flexible microelectronics [1-13]. However, leakage currents and bias effects remain as important challenges to the commercialization of such devices [14-28]. The electrical characterization of novel circuit components, i.e. utilizing field-effect transistor (FET) devices to model new semiconductor materials, can also be confounded by gate leakage and bias stress. The effects can be detrimental, resulting in high OFF currents, low ON/OFF ratios, and increased power consumption. Therefore, leakage current reduction results in the greatest benefit to devices designed for low power and mobile applications, like radio frequency identification tags and autonomous sensors.

The creation of well-defined stable interfaces between inorganic electronic materials and organic electronic systems provides a new range of functionalities. Photovoltaic charge separation can be promoted, transistor threshold voltages can be shifted, and memory effects can be obtained [29-32]. High carrier mobility and transparency in the inorganics can be combined with photosensitivity at desired wavelengths from the organics. The surface chemistry of oxide electronic materials and gate dielectric materials provides important functionality, including photoresponse, environmental sensitivity or protection, and local dipole moments that can dramatically shift electronic properties. For instance, molecules on the surface of n-channel FETs based on zinc oxide (ZnO) and zinc-tin oxide (ZTO) semiconductors can enhance mobility or induce photocurrent [32-36]. However, it remains a challenge to incorporate novel electronic materials in devices without destroying their bulk or surface electronic properties during

processing. Limiting the leakage current through thin gate dielectric layers and isolating adjacent devices are important challenges that must be met before new materials, especially those with surface-induced functionality, can be effectively used in devices. In fundamental studies, the isolation of regions of active material improves the accuracy and reliability of fundamental measurements by reducing leakage current and parasitic bias stress from the semiconducting film surrounding the device [2,3,15,19-22].

Semiconductor thin-films fabricated using solution- or vapor-deposition techniques often produce a thin layer that uniformly covers the entire substrate comprising gate electrode and gate dielectric layers [1-6,8-10,12,14,15]. Multiple devices are created on a single shared semiconductor film, typically by depositing metallic electrodes from vapor through a shadow mask. Such devices mimic conventional metal-oxide-semiconductor (MOS) device structures, and typically utilize standard Si/SiO<sub>2</sub> substrates, which allow equilibration of remotely applied gate voltages with entire arrays of FETs when the silicon is sufficiently doped, and silicon dioxide acts as gate dielectric. The electrical continuity of the semiconducting layer increases parasitic currents between the source/drain electrodes of adjacent FETs, and increases overall surface area in capacitance with other electrodes, like the gate, that want to equilibrate under applied electric fields. In addition, imperfections of the gate oxide, i.e. pinholes or local defects, can result in orders of magnitude increases in leakage current. It is therefore highly desirable to reduce these effects by physically isolating each device.

Different FET configurations and circuit components suffer similar problems, although a few methods have been implemented to mitigate leakage current and unwanted effects, such as engineering device interfaces and geometry [18-28], or implementing biasing/feedback circuits [15-17]. Several strategies exist to mitigate leakage currents via local chemical passivation [26-

28], designed to restrict leakage current through the gate dielectric of thin-film transistors. For instance, self-assembled molecular monolayers (SAMs) provided an electrostatic barrier to leakage currents in n-channel organic semiconductor (OSC) FETs using a dielectric consisting of just 10 nm of silicon dioxide (SiO<sub>2</sub>), which would otherwise have exhibited sufficiently high leakage to make FET operation impossible [26]. The molecular side-chains of the SAM contributed to the capacitance of the gate dielectric and modify the differences in FET operation at millisecond versus ten second gate application times. We recently reported demonstration of OSC molecular segments contributing to the gate capacitance, although they suffered from apparently insufficient dielectric strength and resulted in considerable gate leakage [27]. The parameters of p-channel tellurium-based FETs were similarly modulated using OSC films to shift internal potential differences among layers of the device, and the OSC substantially acts as gate materials in series with the oxide dielectric [28].

Similar effects can be expected with newer high dielectric constant (high-k) dielectrics [37-41]. Enhancing the physical properties of the dielectric may be the best way to mitigate current leaking vertically through the dielectric layer, but it won't necessarily reduce lateral currents. Significantly, a change in dielectric, or modification like SAMs, can affect devices electronically or chemically in potentially undesirable ways, or may be ill-suited for particular applications. For one, high-k dielectrics are shown to reduce charge carrier mobility in OSCs due to random dipole field present at the interface and local polarization effects leading to carrier delocalization [42]. Moreover, thinner dielectrics are more difficult to obtain using large area processing due to uniformity issues and increased risk of pinholes or defects [3]. Clearly there are compromises involved with the choice of gate insulator material and its thickness, which should be deigned to achieve high capacitance density, low gate leakage, and desirable

interfacial chemistry for compatibility with semiconductor materials. Regarding the modeling of FETs, reports that take leakage current into account don't consider isolation by also including active regions beyond the device stack [23-25]. It appears that leakage is not dependent on a particular electronic or chemical property of the dielectric (for voltage potentials below the dielectric breakdown), but instead is mainly dependent on the pinhole/defect density, dielectric thickness, and gate-to-source or gate-to-drain overlap.

Lithography using all solution-processing [15,22], and high-resolution printing methods [39] are presently being developed. As opposed to silicon-based technology which requires high temperatures to fabricate large-area platforms (or handles) of rigid crystalline semiconductor material, devices based on flexible substrates utilize low-temperature processes that allow diverse configurations and complexities to be obtained, including multilayer gate stacks and individually patterned gate electrodes for the fabrication of integrated circuits [18-22]. Individually patterned gate electrodes reduce the risk of leakage current by localizing the applied electric field, which reduces the parasitic capacitances from large areas extending beyond the active device, and potentially reducing parasitic capacitance overlap within the device stack [2,3,14,19-22].

However, there are still drawbacks to these emerging methods, such as alignment issues and chemical requirements [19-22]. Rather than controlling the alignment of gate-to-contact overlap during processing, or depending on additive only processes, patterning can be achieved by removing material from films after their fabrication using 'dry' or 'wet' etch techniques, thus isolating the semiconductor films to their individual device stack. Precise patterning without materials degradation is critically important in applications where several devices must be fabricated using adjacent areas of a conductive film, i.e. when either active layer cannot be

patterned *in situ* of device fabrication with sufficient quality or resolution (such as the active organic semiconductor, dielectric layer, or the Si handle). Lithographic processes are well developed for patterning a variety of inorganic and organic materials but often require multiple chemical steps and can have undesirable effects on electronic materials. For instance, inorganic semiconductors such as ZnO are etched by developers used in photolithography, which can alter the surface chemistry and layer microstructure even when the active ZnO layer is not completely removed. Other materials, such as GaN, resist etching and cannot be patterned by chemical methods.

Together, these previous observations illustrate both the importance and continuing challenge of controlling gate current leakage in semiconductor devices across a wide range of materials systems. Furthermore, other effective strategies for limiting gate leakage must do so without modifying the interface chemical state of the material. We present here a laser directwrite (LDW) processing method and demonstrate it in the isolation of solution-processable hybrid ZnO/organic and vapor-processable Te/OSC field effect devices. LDW utilizes ultrafast pulse duration, particularly valuable for patterning devices while leaving the surface chemistry unchanged for the preservation of device performance, and for the attachment of functional molecules. The physics allow LDW to be applied to semiconductor materials that require or benefit greatly from 'dry' post-processing methods, due to etching sensitivity or etch resistance. Moreover, micro-processing via laser allows us to fabricate semiconductor films under ideal conditions and then pattern a large area, which otherwise would require multiple invasive and complicated steps. Similar laser-based lithographic techniques have gained significant interest as an alternative approach to patterning metallic and dielectric materials with minimal contact [44-63].

Optical pulses with picosecond durations enable high peak powers on the order of 10 MW to be produced with only a few watts of average optical power. Focused radiation can have intensities reaching several TW cm<sup>-2</sup>, which permits direct machining of temperature-sensitive, brittle and soft materials without heating. In addition to materials that have fundamental optical bandgaps with energies lower than the photon energies, materials that are transparent at the laser wavelength can be machined via non-linear absorption. Previous applications of picosecond lasers in micromachining are in medical technology, anti-icing thin-films, optical filters, and circuit components [44-51]. Engelhardt *et al.*, for example, investigated the fundamental processing properties of picosecond laser radiation on stainless steel, alumina, poly(methyl methacrylate), and quartz glass [52]. All the materials they investigated could be ablated efficiently provided that the laser fluence and peak powers were above the ablation threshold of the material while maintaining temperatures below those that would result in thermally driven compositional or microstructural changes.

We investigate two representative systems, including ZnO prepared as a standard transistor semiconductor and in a photomodulatable bilayer with a rhenium bipyridine (Re1c) chromophore, and thin-film bilayers of tellurium (Te) above OSCs. The chemical structures for organic molecules are given in the Supporting Information (Figure S1) [64]. The semiconductor thin-films for this study were deposited on Si/SiO<sub>2</sub> substrates and subsequently source/drain contacts were deposited. Although flexible substrates with a variety of gate/dielectric systems have been developed for electronic applications, the Si/SiO<sub>2</sub> platform remains attractive for semiconductor device testing because of its flatness, relatively dense native surface oxide, and high earth-abundance. Moreover, its standardization and the reputation of SiO<sub>2</sub> as only a marginal quality dielectric provides a platform on which the utility of certain methods for

improving devices may be readily observed. The FET electrode pairs were isolated by optically patterning the semiconductor film using the fundamental wavelength (1030 nm) of a solid-state picosecond laser (Yb-YAG, Hamamatsu Photonics). Detailed experimental conditions for the optical patterning are given in the Methods section.

To determine effects of laser-isolation on FET performance we analyzed the steady-state electronic behavior (field-effect mobility, on/off current ratio, and gate currents) before and after LDW. An explicit lowering of the leakage current is demonstrated by isolation, particularly with ps laser. The only factor that changes due to isolation is reduction in semiconductor area in capacitance with the gate for each device. Reducing the semiconductor area does not directly influence the effective performance parameters of the device, but simply reduces number of pathways for current to leak (vertically through the dielectric to the gate, and laterally along the semiconductor). Conclusions drawn from this report will be applicable to ultrafast laser ablation of active semiconductor materials (organic and inorganic, with various mechanical, chemical, and optical properties), particularly for top-contact bottom-gate FETs but potentially for a wide range of device systems. Besides technical processing advantages, the laser isolation allows the confirmation of key scientific observations otherwise masked (or diminished) by leakage current, including the ZnO photomodulation and the effects of Te-OSC interfacial polarization examples discussed here.

#### II. EXPERIMENTAL METHODS

Heavily As-doped silicon wafers (SI-Tech, Process Solutions,  $N_D \sim 10^{18}$  cm<sup>3</sup>) were cut into one square inch (6 cm<sup>2</sup>) pieces and then cleaned by sonication in deionized water, acetone, and 2-propanol for 10 minutes each, and blowing dry with  $N_2$ . Substrates were cleaned further by submerging in piranha solution (sulfuric acid to hydrogen peroxide 3:1, CAUTION: highly

corrosive and dangerous to skin) for 30 minutes, followed by sonication in deionized water for 10 minutes, blowing with N2 and baking on a hotplate at 110 °C for 5 minutes. The insulator capacitance for 100 and 300 nm of thermally grown silicon dioxide is consistent with previous reports, 35.6 and 11.5 nF/cm<sup>2</sup>, respectively. 6PTTP6 was synthesized using a well-established method [65]. Te powder (325-mesh, 99.99% metals basis, Alfa Aesar) was used as purchased. Hybrid bilayer FETs were fabricated by thermally evaporating OSC and Te powders using an Edwards thermal evaporation system at pressures below 5x10<sup>-6</sup> Torr, deposited 10 nm thick from alumina crucibles in succession during the same vacuum cycle, using the same deposition rate of 0.3 Å s<sup>-1</sup>. Si substrates with 100 nm of SiO<sub>2</sub> were held at 55 °C during deposition. Gold or aluminum electrodes were deposited 50-100 nm thick at 0.5 Å s<sup>-1</sup> through a shadow mask. The channel width and length is about 8000 and 250 µm, respectively, for Te/OSC hybrids, and are 1000 and 100 µm, respectively, for ZnO devices. Deposition rates and thicknesses were monitored by quartz crystal microbalance. Substrate temperature was monitored by thermocouples placed on the substrate backside. Silicon gates for FETs were accessed by scratching through the oxide with a diamond scribe.

ZnO precursor solution consists of 0.3 M zinc acetate dihydrate (Alfa Aesar) dissolved in absolute ethanol with 0.3 M of acetylacetone added as a stabilizer (adapted from ref. 8). The precursor solution was stirred overnight at room temperature and filtered through a 0.2 μm polytetrafluoroethylene (PTFE) filter. As-prepared precursor solution was kept for 24 hours to promote hydrolysis and filtered through a 0.45 μm PTFE filter. ZnO solutions were deposited onto 300 nm SiO<sub>2</sub> by spin coating at 5000 revolutions per minute for 30 seconds followed by heating to 75 °C for 10 minutes to evaporate residual solvent. The films were annealed in air at 500 °C for 1 hour. The coating process was repeated in three consecutive cycles of spin coating

and heat treatment. The heat treatment converts the zinc acetate precursor into ZnO and improves the crystallinity of the film. The ZnO layer exhibits a crystallographic texture in which the c-axis is along the surface normal of the substrate. The surface of pre-fabricated ZnO FET samples was sensitized with the Re1c dye molecules by immersion in 5 mL of a 1 mM solution of Re1c dye in THF at room temperature for 24 hours. The vials containing the samples were covered in foil during immersion to block light. After immersion the samples were rinsed with 5-10 ml of pure THF without allowing the dye solution to dry on the sample surface, and then blown dry with a high-purity nitrogen gun.

Amplified Yb:YAG picosecond laser pulses (MOIL-ps, Hamamatsu Photonics), pulse duration ca. 1.5 ps, 1030 nm wavelength, and 40 kHz repetition rate were used to process the hybrid structures. For other samples, the wavelength can be selected to up to the fourth harmonic to achieve maximum absorption. The laser pulses were focused on the sample surface using an acromatic lens with a focal length of 60 mm delivering a focused beam spot with diameter of approximately 25 um and laser fluence of 0.09 J cm<sup>-2</sup> for the hybrid material. The sample was located on a XYZ translation stage and scanned at 480 mm/min. **Table I** shows the beam parameters used for laser processing and the pertinent specifications of the Hamamatsu Photonics MOIL laser L11590. This laser has a tunable pulse duration capability (from 1.5 to 10 ps) and high energy per pulse ( $200 \mu J$ ). Typically picosecond lasers only achieve low energy per pulse ( $200 \mu J$ ), and rely on high repetition rates to increase peak power.

FET measurements, taken before and after isolation, were employed using an Agilent 4155C Semiconductor Parameter Analyzer. Low-resistance probes from Micromanipulators were used to contact devices under ambient fluorescent lighting conditions, in air.

#### III. FET ISOLATION IMAGING

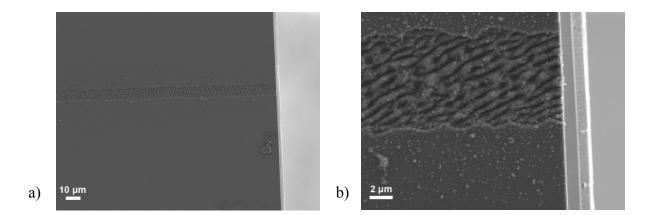

Trenches created by picosecond-laser patterning were imaged using laser optical microscopy, scanning electron microscopy (SEM), and atomic force microscopy (AFM). The images and height profiles show that the laser patterning physically isolates transistors from the shared semiconductor film. The physical mechanism of the patterning varied for different semiconductor layers. The ZnO semiconductor layer and SiO<sub>2</sub> gate insulator of the ZnO FETs both have bandgaps larger than the fundamental 1030 nm wavelength of the Nd:YAG picosecond laser. A large fraction of the incident optical power during patterning is thus transmitted to the Si substrate. In ZnO the rapid ablation of the Si ruptures the SiO<sub>2</sub> and ZnO layers, creating the trenches shown in the SEM images in Figure 1. The bottoms of the trenches in Si exhibit a pattern of ridges consistent with interface instabilities observed in rapid solidification of laser-melted Si [57,58].

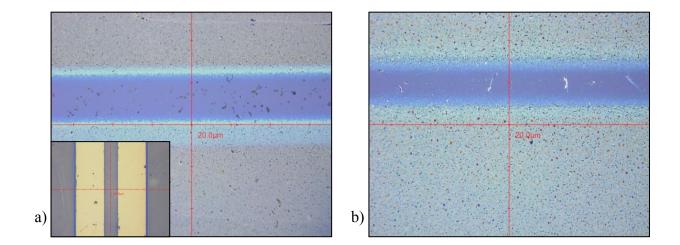

The mechanism for laser patterning and subsequent isolation of Te FET was different from that of the ZnO devices. Sufficient optical power was absorbed in Te to ablate the Te layer before damaging the underlying  $SiO_2$  or Si. Figure 2 shows bright-field optical micrographs of the regions patterned using the picosecond laser. Inspection of the ablated surface reveals that the Te and OSC layers are completely removed by the patterning. Atomic force microscopy confirms the removal of the approximately 10 nm Te as well as the 20 nm of 6PTTP6, underlying it, while the dielectric surface remains intact (Figure S2) [64]. The trenches in Tebased devices are 10 - 30 nm deep, which is the approximate thickness of semiconductor stacks. The edge roughness is less than 1  $\mu$ m and burrs are not apparent on the Te surface. It is therefore

relatively straightforward to remove Te films selectively at low ablation thresholds without damaging the SiO<sub>2</sub> dielectric.

The width of fabricated channels matches the diameter of the pulse beam in the case of Te-based devices,  $25~\mu m$ , and was thinner for zinc oxide-based devices,  $10~\mu m$ . In both cases, some of the material removed from the trenches was deposited as submicron debris in the surrounding areas. Channel widths obtained by hand-isolation, via scribing around devices with hard tools or using paint brushes carrying solvent could not be reduced below  $100~\mu m$  due to the width of the scribing tools.

#### IV. FET ANALYSIS AND DISCUSSION

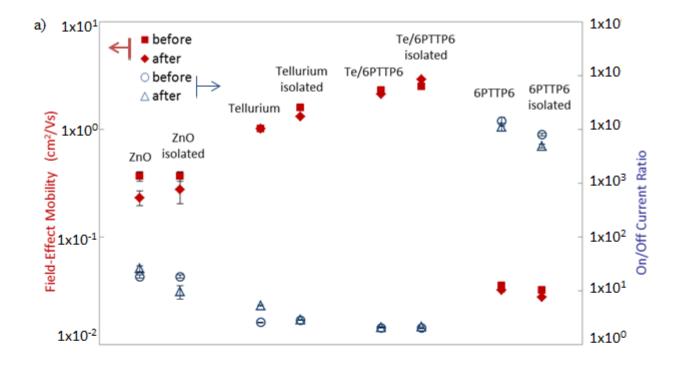

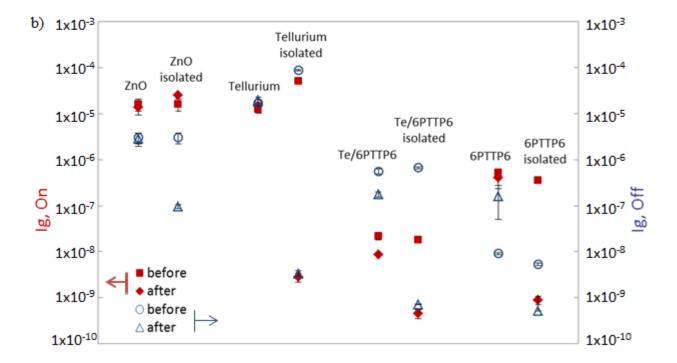

FET device parameters such as field-effect mobility ( $\mu$ ), threshold voltage ( $V_{th}$ ), gate current ( $I_G$ ) and the ratio of on to off drain current ( $I_{on}/I_{off}$ ) were measured before and after isolation. Tables SI and SII of the Supporting Information [64] list the performance parameters of all FETs before and after LDW and after scribing for comparison. Identical control devices were stored for the same time interval but did not undergo isolation. The electronic effects of hand isolation are essentially reproduced by LDW. Isolation by either method reduces  $I_G$  while not altering the critical parameters, such as field-effect  $\mu$  and  $I_{on}/I_{off}$ . Figure 3(a) shows graphically that the critical FET parameters are essentially unchanged by LDW for zinc-oxide and tellurium-based devices.  $I_G$  of FETs in both the on and off operation are shown separately in Figure 3(b) for zinc-oxide and tellurium-based devices.

We observe that all parameters (mobility, on/off ratio, and gate currents) depend on the semiconductor material, and that isolation treatment only affects the gate current by reducing it to a minimal value. The final gate leakage currents depend on the parasitic source/gate and

drain/gate overlap, and on the number of defects/pinholes in the dielectric that remain in the gate stack after isolation treatment.

#### A. Zinc oxide-based FETs

ZnO forms n-channel accumulation mode transistors. After LDW, the measured I<sub>G</sub> is reduced in the OFF mode by almost two orders of magnitude (Figure 3(b)). There is still relatively large leakage in ZnO devices at high gate voltages (50 V), which may be due to leakage at high fields in the regions directly beneath the source/drain electrodes or FET channel.

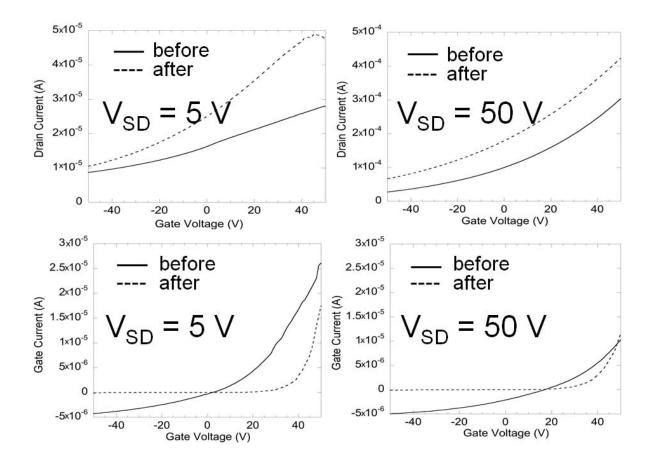

Figure 4 shows the transfer curves and  $I_G$  for ZnO devices before and after isolation, with  $V_{SD} = 5$  and 50 V. The drain current is enhanced by isolation due to fewer current losses by leakage, which accounts for the slight decrease in on/off ratio (FIG 3(a)). Figure 4 also shows that dielectric breakdown occurs after 40  $V_G$ , but that isolation minimizes gate leakage over the rest of the gate voltage range.  $I_G$  for on mode ZnO devices is greater after isolation according to FIG 3(b) only because the value used was taken at  $V_G = 50$  V, whereas the  $I_G$  due to isolation is actually much lower for applied gate voltages below the dielectric breakdown. This is acceptable because isolation does not reduce vertical leakage current from the gate drain/source overlap, which would increase drastically during dielectric breakdown as observed. LDW only reduces lateral currents due to an extended semiconductor film gate stack, and vertical pathways beyond the gate stack.

Nonchemical isolation methods are particularly useful for ZnO devices because chemical etching, usually with acid, can modify ZnO/molecular interfaces. The vapor transport of the etchant can result in interface modification within regions of the film separated from the etched regions up to distances of millimeters or more. The oganometallic donor Re1c can be attached to ZnO, and used to donate electrons to ZnO following optical excitation. [36]. Here we illustrate

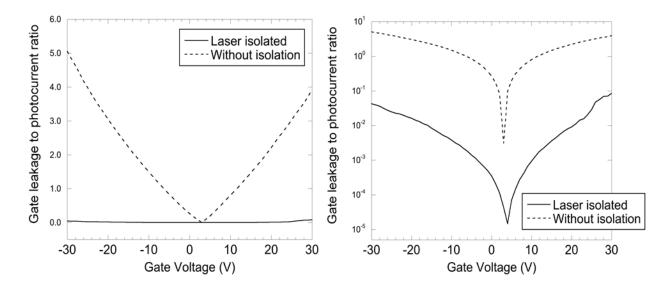

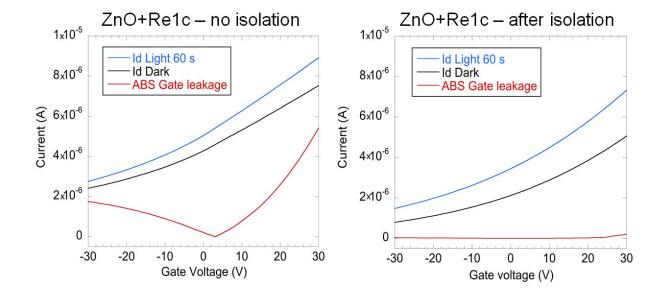

the importance of non-chemical isolation by examining the photocurrent response for Relc-functionalized ZnO FETs that are isolated by laser ablation and compare to control devices which are not isolated. The drain and gate currents were measured in the dark, then again after exposing the FET channel to light ( $\lambda$  = 532 nm) for 60 seconds. Prior to isolation the leakage current is on the same order magnitude as the drain current (greater than 5  $\mu$ A at gate voltage of 30 V), as expected because the relatively high mobility in the ZnO layer allows leakage current from a large area of the dielectric to contribute. The leakage  $I_G$  is greater than the photocurrent by a factor of four under this forward bias condition ( $V_G$  = 30 V). After LDW, the magnitude of the  $I_G$  is reduced to less than 1% of the magnitude of the photocurrent. Figure 5 shows the ratio of  $I_G$  to photocurrent for devices that were not isolated and devices isolated by LDW. Figure 6 shows the transfer curves and  $I_G$  for ZnO/Re1c devices with and without isolation. The isolation procedure could greatly enhance the possibilities for use of organic-inorganic hybrids for photodetector applications.

As an alternative to LDW, FET devices can be isolated by locally etching the ZnO films with a mild acid, such as acetic acid. Chemical isolation using acetic acid and a paint brush was more effective than laser-processing for eliminating gate leakage in zinc oxide films (reduced more than 5 orders of magnitude, Figure S3 [64]). This could be due to the fact that the excess ZnO semiconductor material is removed from around and between FETs while the underlying SiO<sub>2</sub> gate dielectric is undamaged by the comparatively mild acid etching. However, vapors from the acetic acid etching process can uncontrollably change the conductivity of the ZnO film remaining in the channel, as well as possibly affecting attachment of donor molecules on the surface by blocking attachment sites for the carboxylic acid groups [33]. Additionally, this form

of hand-isolation for research devices is not scalable as a high-throughput isolation method for manufacturing arrays of many devices.

### B. Tellurium and organic-based FETs

Elemental tellurium behaves as a p-channel depletion mode transistor, which means the FET is inherently on at zero gate voltage ( $V_G$ ) and requires positive  $V_G$  to turn the device off. The gate voltage required to turn off FETs is approximately 40-50 V for our 10 nm of Te deposited (0.3 Ås<sup>-1</sup>) onto SiO<sub>2</sub> substrates held at 60 °C. 6PTTP6 is also p-channel and was deposited under the same conditions. 6PTTP6, however, operates in accumulation and only requires negative  $V_G$ . The drain voltage ( $V_D$ ) for all 6PTTP6 and Te devices was swept from 0 to -20 V for measuring output curves and held at -20 V for transfer curves.

6PTTP6 devices that were not isolated showed slight increase in off-state  $I_G$  over time (Figure 3(b)), while the on-state  $I_G$  was constant. Laser isolation reduced  $I_G$  significantly for both cases, and did so more effectively than mechanical isolation (Table SII [64]), even though there is the possibility that laser processing may eject positive Si ions from the oxide and could cause buildup of electrical charge [59,62]. In Te FETs,  $I_G$  is drastically reduced (4 orders of magnitude) by sandwiching an OSC layer between Te and the dielectric, and lateral field-effect mobility is enhanced by the OSC, as we noticed previously [28]. The isolation of Te alone results in  $I_G$  less than Te/6PTTP6 not-isolated (5 orders of magnitude reduction), but the Te/6PTTP6 bilayer after isolation, in the on state, had the lowest  $I_G$  of all. The transfer curves and  $I_G$  for representative Te and Te/6PTTP6 devices, before and after isolation, are shown in the Supporting Information (Figure S4 [64]). Note the lower current scale for the  $I_G$  plot after isolation.

The data points in Figure 3(b) show, counterintuitively, that the on-state leakage current for non-isolated Te/6PTTP6 is considerably lower than for 6PTTP6 alone, even though the Te could greatly expand the area over which leakage could occur because of its much higher conductivity than that of 6PTTP6. It is not clear from the data whether this effect is because of an attribute of the entire film area, or of a few distributed defective points. The fact that the lower bilayer on-state leakage current is observed in a set of *isolated* devices as well is evidence for this being characteristic of the *entire film*, since the effect is observed at multiple arbitrary locations. This conclusion could not have been reached without the isolation procedure.

Note that the off-state  $I_G$  is not lower for the bilayer. We attribute this to a polarity resulting from hole transfer between Te and 6PTTP6 resulting in an interfacial dipole with the positive end at Te and the negative end at 6PTTP6 [28]. This dipole indicates depletion of holes in the 6PTTP6, and the on-state gate-to-source voltage, with the gate more negative, would deplete these holes further, and  $I_G$  would decrease. On the other hand, the off-state voltage, where the gate is positive, would reinject holes into the 6PTTP6 and  $I_G$  would increase. A similar current-blocking effect was observed for interfaces between Te and aluminum due to diffusion of oxygen through Te grain boundaries and to the semiconductor-metal interface [63]. Injection barriers commonly form due to chemical defects or oxidation between conjugated organic semiconductors and metals, particularly from metals deposited onto OSCs by vapor, but the barriers are typically difficult to observe due to low bulk currents in OSCs [66-69]. In terms of applications, the isolation procedure is clearly helpful in enabling the use of field-effect devices made from low bandgap or extrinsically conductive semiconductors.

### V. CONCLUSIONS

Isolation is critically important for devices where sensitivity and high signal-to-noise at low power are required. LDW methods are extremely reproducible, and negligible variation in microstructural (i.e. trench depth, line-edge roughness) or FET parameters (i.e. field-effect  $\mu$ ) was observed between samples. Gate leakage is significantly reduced by LDW for the devices that we examined here, at least by the geometric area reduction of 2-3 orders of magnitude. LDW is shown to be an effective alternative for removing selected domains of both soft semiconductors and metal oxides of certain relative hardness compared to that of the dielectric, a useful alternative for materials that can be easily damaged by photolithography and chemical etchants. The measured photocurrent for ZnO devices functionalized with donor molecules was initially masked by significant gate leakage current, and that photocurrent is substantially enhanced by the donor as deposited. Similarly, we emphasized that removing parasitic currents allows us to more clearly observe effects and behavior of the intrinsic dipole due to energy alignment of Te-OSC heterojunctions.

Preservation of lifetime characteristics, yield, and performance for devices using semiconductors other than Si will be driven by processing solutions which limit adverse thermal and chemical effects, while providing automation and high volume scaling. LDW can be all automated and is scalable because successive beam-splitters can be used to simultaneously pattern multiple arrays of circuits in parallel [70]. Ultrafast pulses allow for non-invasive and selective material ablation, ensuring a clean and precise isolation technique which improves FET electrical performance and eases FET performance assessment, thus making LDW a viable patterning alternative.

**Acknowledgment.** We thank Patricia McGuiggan and Josué F. Martínez Hardigree for assistance with AFM measurements. We are grateful for the following project funding: National Science Foundation Division of Materials Research (DMR), MRSEC program, grant number 1121288 (ZnO interface and photocurrent), and the Department of Energy, Office of Science, Basic Energy Sciences, grant number DE-FG02-07ER46465 (organic interface and tellurium work). We thank Professor Padma Gopalan for supplying the organometallic dye.

**Author Contributions.** Katz, Ireland, and Liu made transistor devices, and acquired and analyzed I-V data under various conditions. Spalenka and Evans made ZnO devices, attached and synthesized dye, and measured currents including photocurrents. Jaiswal, Fukumitsu, and Oishi performed laser-isolation experiments.

#### REFERENCES

- 1. G. Horowitz, Organic field-effect transistors, Adv. Mater. 5, 10, (1998).

- B. Crone, A. Dodabalapur, Y. Y. Lin, R. W. Filas, Z. Bao, A. LaDuca, R. Sarpeshkar, H. E. Katz, W. Li, Large-scale complementary integrated circuits based on organic transistors. Nature 403, 521 (2000).

- 3. C. D. Dimitrakopoulos and P. R. L. Malenfant, Organic thin film transistors for large area electronics. Adv. Mater. 2, 14, (2002).

- T. Someya, T. Sekitani, S. Iba, Y. Kato, H. Kawaguchi, and T. Sakurai, A large-area, flexible pressure sensor matrix with organic-field-effect transistors for artifical skin applications.

Proc. Natl. Acad. Sci. USA 101, 9966 (2004).

- 5. G. H. Gelinck *et al.*, Flexible active-matrix displays and shift registers based on solution-processed organic transistors. Nat. Mater. **3**, 106 (2004).

- 6. K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature. **18**, 2448 (2004).

- V. Subramanian, J. M. J. Frechet, P. C. Chang, D. C. Huang, J. B. Lee, S. E. Molesa, A. R. Murphy, D. R. Redinger, Progress towards development of all-printed RFID tags: Materials, processes, and devices. Proc. IEEE 93, 1330 (2005).

- 8. L. Torsi, G. M. Farinola, F. Marinelli, M. C. Tanese, O. H. Omar, L.Valli, F. Babudri, F. Palmisano, P. G. Zambonin, F. Naso, A sensitivty-enhanced field-effect chiral sensor. Nat. Mater. 7, 412 (2008).

- 9. S. H. Ko, I. Park, H. Pan, N. Misra, M. S. Rogers, C. P. Grigoropoulos, and A. P. Pisano, ZnO nanowire network transistor fabrication on polymer substrate by low-temperature, all-inorganic nanoparticle solution process. Appl. Phys. Lett. **92**, 154102 (2008).

- 10. C. S. Li, Y. N. Li, Y. L. Wu, B. S. Ong, and R. O. Loutfy, Fabrication conditions for solution-processed high-mobility ZnO thin-film transistors. J. Mater. Chem. **19**, 1626 (2009).

- 11. J. Sun, B. Zhang, and H. E. Katz, Materials for printable, transparent, and low-voltage transistors. Adv. Func. Mater. **21**, 29 (2011).

- 12. B. D. Ahn, H. J. jeon, and J.S. Park, Effects of Ga:N addition on the electrical performance of zinc tin oxide thin film transistor by solution-processing. ACS Applied Mater. And Interfaces **6**, 9228-9235 (2014).

- 13. I. Mejia, A. L. Salas-Villasenor, A. Avendano-Bolivar, J. Horvath, H. Stiegler, B. E. Gnade, and M. A. Quevedo-Lopez, Low-temperature hybrid CMOS circuits based on chalcogenides and organic TFTs. IEEE Electron Device Letters 32, 1086-88 (2011).

- 14. <u>B. M. Dhar, R. Özgün, T. Dawidczyk, A. Andreou, H. E. Katz, Threshold voltage shifting for memory and tuning in printed transistor circuits. Mater. Sci. Eng. R 72, 49 (2011).</u>

- 15. Hagen Klauk, in *Proceedings of the IEEE <u>Device Research Conference</u> on Organic complementary circuits scaling towards low voltage and submicron channel length, <i>University Park*, 2012.

- 16. W. Huan, W. Zhigong, F. Jun, L. Wenyuan, W. Rong, and M. Peng, A pixel circuit with reduced switching leakage for an organic-light-emitting diode. J. Semiconductors 33, 125006 (2012).

- 17. A. K. Rana, N. Chand, and V. Kapoor, Gate leakage aware optimal design of modified hybrid nanoscale MOSFET and its application to logic circuits. Iranian Journal of Electrical and Electronic Engineering 7, 2, (2011).

- 18. W. Xu and S.W. Rhee, Compromise of electrical leakage and capacitance density effects: a facile route for high mobility and sharp subthreshold slope in low-voltage operable organic filed-effect transistors. J. Mater. Chem. **21**, 998 (2012).

- 19. C.M. Keum, J.H. Bae, M.H. Kim, W. Choi, and S.D. Lee, Solution-processed low leakage organic field-effect transistors with self-pattern registration based on patterned dielectric barrier. Org. Elec. **13**, 778 (2012).

- 20. K. Rana, N. Chand, and V. Kapoor, Gate leakage reduction through the use of a gate-to-source/drain non-overlapped metal-oxide-semiconductor field-effect transistor structure. Journal of Nanoengineering and Nanosystems 224, (2010).

- 21. T. Zaki, R. Rodel, F. Letzkus, H. Richter, U. Zschieschang, H. Klauk, J. N. Burghartz, AC characterization of organic thin-film transistors with asymmetric gate-to-source and gate-to-drain overlaps. Org. Elect. 14, 1318-1322 (2013).

- 22. K. C. Dickey, S. Subramanian, J. E. Anthony, L.H. Han, S. Chen, and Y.L. Loo, Large-area patterning of solution-processable organic semiconductor to reduce parasitic leakage and off currents in thin-film transistors. Applied Physics Letters **90**, 244103 (2007).

- 23. H. Jia. G. K. Pant, E. K. Gross, R. M. Wallace, B. E. Gnade, Gate induced leakage and drain current offset in organic thin film transistors. Org. Elect. 7, 16-21 (2006).

- 24. J. F. Conley, Instabilities in amorphous oxide semiconductor thin-film transistors. IEEE Transactions on Devices and Materials Reliability 10, 460-475 (2010).

- 25. S. Hengen, M. Alt, G. Hernandez-Sosa, J. Giehl, U. Lemmer, and N. Mechau, Modelling and simulation of gate leakage currents of solution-processed OTFT. Org. Elect. 15, 829-834 (2014).

- 26. J. F. M. Hardigree, T. J. Dawidczyk, R. M. Ireland, G. L. Johns, B.J. Jung, M. Nyman, R. Osterbacka, N. Markovic, and H. E. Katz, Reducing leakage currents in n-channel organic field-effect transitors using molecular dipole monolayers on nanoscale oxides. Appl. Mater. Inter. 5, 7025 (2013).

- 27. B. J. Jung, J. F. M. Hardigree, B. M. Dhar, T. J. Dawidczyk, J. Sun, K. C. See, and H. E. Katz, Naphthalenetetracarboxylic diimide layer-based transistors with nanometer oxide and side chain dielectrics operating below one volt. ACS Nano 5, 2723 (2011).

- 28. R. M. Ireland, T. J. Dawidczyk, P. Cottingham, T. McQueen, G. Johns, N. Markovic, L. Zhang, P. Gopalan, and H. E. Katz, Effects of pulsing and interfracial potentials on tellurium-organic heterostructured film. Appl. Mater. Inter. 5, 1604 (2013).

- S. Kobayashi, T. Nishikawa, T. Takenobu, S. Mori, T. Shimoda, T. Mitani,

H. Shimotani, N. Yoshimoto, S. Ogawa, and Y. Iwasa, Control of carrier density by self-assembled monolayers in organic field-effect transistors. Nature Materials 3, 317 (2004).

- 30. P. Paoprasert, B. Park, H. Kim, P. Colavita, R. J. Hamers, P. G. Evans, and P. Gopalan, Dipolar cromophore functional layers in organic field-effect transistors. Adv. Mater. 20, 4180 (2008).

- 31. B. Park, S. Choi, S. Graham, and E. Reichmanis, Memory and photovoltaic elements in organic filed-effect transistors with donor/acceptor planar-hetero junction interfaces. J. Phys. Chem. **116**, 9390 (2012).

- 32. Bo Zhang, Y, Liu, S. Agarwal, M.L. Yeh, and H. E. Katz, Structure, sodium ion role, and practical issues for beta-alumin as high-k dielectric solution-processed gate layer for transparent low-voltage electronics. ACS Appl. Mater. Interfaces **3**, 4254 (2011).

- 33. J.W. Spalenka, P. Gopalan, H.E. Katz, and P.G. Evans, Electron mobility enhancement in ZnO thin films via surface modification by carboxylic acids. Appl. Phys. Lett. **102**, 041602 (2013).

- 34. P. Paoprasert, J. E. Laaser, W. Xiong, R. A. Franking, R. J. Hamers, M. T. Zanni, J. R. Schmidt, and P. Gopalan, Bridge-dependent interfacial electron transfer from rhenium-bipyridine complexes to TiO2 nanocrystalline thin films. J. Phys. Chem. C **114**, 9898 (2010).

- 35. P. Paoprasert, S. Kandala, D. P. Sweat, R. Ruther, and P. Gopalan, Versatile grafting chemistry for creation of stable molecular layers on oxides. J. Mater. Chem. **22**, 1046 (2012).

- 36. J. W. Spalenka, Y. Joo, R. M. Ireland, P. Gopalan, H. E. Katz, and P. G. Evans, (unpublished, in preparation).

- 37. B. N. Pal, B. M. Dhar, K. C. See, and H. E. Katz, Solution-deposited sodium beta-alumina gate dielectrics for low-voltage and transparent field-effect transistors. Nat. Mater. **8**, 898 (2010).

- 38. Y. Su, C. Wang, W. Xie, F. Xie, J. Chen, N. Zhao, and J. Xu, Low-voltage organic field-effect transistors with solution-processed metal-oxide as gate dielectric. Appl. Mater. Inter. 3, 4662 (2011).

- 39. Y. M. Park, A. Desai, and A. Salleo, Solution-processsable zirconium oxide gate dielectrics for flexible organic field effect transistors operated at low voltages. Chem. Mater. **25**, 2571 (2013).

- 40. J. Peng, Q. Sun, S. Wang, H.Q. Wang, and W. Ma, Low-temperature solution-processed alumina as gate dielectric for reducing the operating-voltage of organic field-effect transistors. Appl. Phys. Lett. **103**, 061603 (2013).

- 41. R. P. Ortiz, A. Fachetti, and T. J. Marks, High-k organic, inorganic, and hybrd dielectrics for low-voltage organic field-effect transistors. Chem. Rev. **110**, 205 (2010).

- 42. J. Veres, S. D. Ogier, S. W. Leeming, D. C. Cupertino, and S. M. Khaffaf, Low-k insulators as the choice of dielectrics in organic field-effect transistors. Adv. Funct Mater. 13, 199 (2003).

- 43. P. F. Moonen, I. Yakimets, and J. Huskens, Fabrication of transistors on flexible substrates: from mass-printing to high-resolution alternative lithography strategies. Adv. Mater. (2012).

- 44. P. Tormala, T. Pohjonen, and P. Rokkanen, Bioabsorbable polymers: Materials technology and surgical applications. J. Eng. Med. **212**, 101 (1998).

- 45. D. Analdo del Cerro, G.R.B.E.R. Omer, and A.J. Huis Veld, Picosecond laser machined designed patterns with anti-ice effect, in *Proceedings of the 11<sup>th</sup> International Symposium on Laser Precision Microfabrication, Stuttgart, 2010.*

- 46. M. D. Perry, B. C. Stuart, P. S. Banks, M. D. Feit, V. Yanovsky, and A. M. Rubenchik, Ultrashort-pulse laser machining of dielectric materials. J. Appl. Phys. **85**, 6803 (1999).

- 47. V. V. Rana and Z. Zhang, Selective removal of dielectric layers using picoseconds UV pulses in *Proceedings of the SPIE Conference on Solid State Lasers XVIII: Technology and Devices, San Jose*, 2009.

- 48. J. Kruger, M. Lenzner, S. Martin, M. Lenner, C. Spielmann, A. Fiedler, and W. Kautek, Single- and multi-pulse femotosecond laser ablation of optical filter materials. J. Appl. Surf. Sci. **208**, 233 (2003).

- 49. F. Haase, E. G. Rojas, K. Bothe, and R. Brendel, Layer selective laser ablation for local contacts to thin emitters. Energy Procedia 8, 577 (2011).

- 50. R. Mandamparambil, H. Fledderus, G. Van Steenberge, and A. Dietzel, Patterning of Flexible Organic Light Emitting Diode (FOLED) stack using an ultrafast laser Optics Express 18, 7575 (2010).

- 51. J. Bonse, G. Mann, J. Kruger, M. Marcinkowski, and M. Eberstein, Femtosecond laser-induced removal of silicon nitride layers from doped and textured silcon wafers used in photovoltaics. Thin Solid Films 542, 420 (2013).

- 52. U. Engelhardt, J. Hildenhagen, and K. Dickmann, Micromachining using high-power picosecond lasers: comparison of various materials. Micro Mater. Proc. 5, 32 (2011).

- 53. P. Balling and J. Schou, Femtosecond-laser ablation dynamic of dielectrics: basics and applications for thin films. Rep. Prog. Phys **76**, 036502, (2013).

- 54. C. Momma, S. Nolte, B. N. Chichkov, F. v. Alvensleben, A. Tunnermann, Precise laser ablation with ultrashort pulses. Applied Surface Science **109**, 110, (1997).

- 55. G. Raciukaitis, M. Brikas, M. Gedvilas, and G. Darcianovas. Patterning of ITO layer on glass with high repetition rate picosecond lasers. Journal of Micro/Nnaoengineering **2**, 1 (2007).

- 56. A. Ben-Yakar and R. L. Byer, in Proceedings of SPIE on Femtosecond laser machining of fluidic microchannels for miniaturized bioanalytical systems, San Jose, 2002.

- 57. Y.F. Lu, W.K. Choi, Y. Aoyagi, A. Kinomura, and K. Fujii, Controllable laser-induced periodic structures at silicon-dioxide/silicon interface by excimer laser irradiation. J. Appl. Phys. **80**, 7052 (1996).

- 58. A.J. Pedraza, Y.F. Guan, J.d. Fowlkes, and D.A. Smith, Nanostructures produced by ultraviolet laser irradiation of silicon. J. Vac. Sci Tech. B **22**, 2823 (2004).

- 59. N. M. Bulgakova, R. Stoian, A. Rosenfeld, I. V. Hertel, and E. E. B. Campbell, Electronic transport and consequences for material removal in ultrafast pulsed laser ablation of materials. Phys. Rev. B **69**, 054102 (2004).

- 60. A. Tunnermann, S. Nolte, and J. Limpert, Femtosecond vs. picosecond material processing: Challenges in ultrafast precision laser micro-machining of metals at high repetition rates. Ultrashort Pulses 1, 34 (2010).

- 61. J. Cheng, C.S. Liu, S. Shang, D. Liu, W. Perrie, G. Dearden, K. Watkins, A review of ultrafast laser materials machining. Optics Laser Tech. 46, 88 (2013).

- 62. R. Stoian, A. Rosenfeld, D. Ashkenasi, I. V. Hertel, N. M. Bulgakova, and E. E. B. Campbell, Surface charging and impulsive ion ejection during ultrashort pulsed laser ablation, in *Proceedings of the SPIE Conference on Commercial and Biomedical Applications of Ultrafast Lasers V, San Jose, 2005*.

- 63. N. M. Bulgakova, V. P. Zhukov, W. Marine, A. Y. Vorobyev, and C. Guo, Charging effects under ultrashort pulsed laser ablation, in *Proceedings of the SPIE Conference on High-Power Laser Ablation VII*, Taos, 2008.

- 64. See Supplemental Material at [URL will be inserted by publisher] for chemical structures, an AFM of a trench ablation, and additional gate current plots.

- 65. H.E. Katz, T. Siegrist, B. Ocko, M. Lefenfeld, P. Gopalan, P.; and M. Mushrush, Mesophase transitions, surface functionalization, and growth mechanism of semiconducting 6PTTP6 films from solution. J. Phys. Chem. 108, 8567-8571 (2004).

- 66. K. Okuyama, J. Tsuhako, and Y. Kumagai, Behavior of metal contacts to evaporated tellurium films. Thin Solid Films **30**, 119 (1975).

- 67. H. Ishii, K. Sugiyama, E. Ito, and K. Seki, Energy level alignment and interfacial structures at organic/metal and organic/organic interfaces. Adv. Mater. **11**, 606 (1999).

- 68. A. Crispin, A. Jonsson, M. Fahlman, and W. R. Salaneck, Aluminum-barium interfaces on some processable poly(p-phenylene vinylene) polymers studied by photoelectron spectroscopy. J. Chem. Phys. **115**, 5252 (2001).

- 69. J. Hwang, A. Wan, and A. Kahn, Energetics of metal-organic interfaces: New experiments and assessment of the field. Mater. Sci. Eng. R 64, 1 (2009).

- 70. Z. Kuang, W. Perrie, D. Liu, S. P. Edwardson, Y. Jiang, E. Fearon, K. G. Watkins, and G. Dearden, Ultrafast laser parallel microprocessing using high uniformity binary Dammann grafting generated beam array. Appl. Surf. Sci. (2013).

### **Tables and Figures.**

Table I. Optical Beam Parameters

| Wavelength            | 1030 nm                          |

|-----------------------|----------------------------------|

| Rep. Rate, Scan Speed | 20 kHz, 480 mm min <sup>-1</sup> |

| Spot Size             | 25 μm                            |

| Pulse Duration        | 1.5 ps                           |

| Fluence               | $0.09 \pm 4 \text{ J cm}^{-2}$   |

| Peak Power            | 0.24 MW                          |

| Min Spot Size         | 1.5 μm                           |

- FIG. 1. Scanning electron micrographs of a) laser-isolated microchannel running up to freshly cleaved edge of the chip (scale bar 10  $\mu$ m) and b) magnification of previous region near the edge (scale bar 2  $\mu$ m).

- FIG. 2. Color optical microscope images show microchannels in a) Te, inset shows channels in Te alongside the gold electrode pair, and b) Te/6PTTP6.

- FIG. 3. Comparison chart for a) field-effect mobility (left axis) and on/off current ratio (right axis) and b) gate current in the on mode (left axis) and off mode (right axis) for zinc-oxide, tellurium-based, and organic semiconductors devices. Values for identical sample sets are shown

in vertically aligned points; sample sets are labeled above from left to right; each point is an average of 12 devices. "Before" and "after" refer to measurements taken before and after laser-isolation; values are given for both non-isolated and "isolated" sample sets. The lower value of red diamond and blue triangle values (compared to red square and blue circle values, respectively) for "isolated" systems indicates the beneficial effect of the isolation.

FIG. 4. Transfer curves and  $I_G$  for ZnO devices before and after isolation, with  $V_{SD}$  equal to a) 5 V and b) 50 V.

FIG. 5. Linear plot and log plot of measured gate leakage to photocurrent ratio in a representative ZnO/Re1c FET. Solid curves for sample isolated by laser; dot-dashed curves for not isolated.

FIG. 6. Transfer curves for photomodulatable ZnO FETs with gate leakage, for devices without and with isolation.