# CHCRUS

This is the accepted manuscript made available via CHORUS. The article has been published as:

### Low-Resistance, High-Yield Electrical Contacts to Atom Scale Si:P Devices Using Palladium Silicide

Scott W. Schmucker, Pradeep N. Namboodiri, Ranjit Kashid, Xiqiao Wang, Binhui Hu, Jonathan E. Wyrick, Alline F. Myers, Joshua D. Schumacher, Richard M. Silver, and M. D. Stewart, Jr.

> Phys. Rev. Applied **11**, 034071 — Published 29 March 2019 DOI: 10.1103/PhysRevApplied.11.034071

## Low-resistance, high-yield electrical contacts to atom scale Si:P devices using palladium silicide

Scott W. Schmucker<sup>1\*</sup>, Pradeep N. Namboodiri<sup>2</sup>, Ranjit Kashid<sup>2</sup>, Xiqiao Wang<sup>1</sup>, Binhui Hu<sup>1</sup>, Jonathan E. Wyrick<sup>2</sup>, Alline F. Myers<sup>2</sup>, Joshua D. Schumacher<sup>2</sup>, Richard M. Silver<sup>2</sup>, M.D. Stewart, Jr.<sup>2†</sup>

<sup>1</sup>University of Maryland, College Park, Maryland 20742, USA

<sup>2</sup>National Institute of Standards & Technology, Gaithersburg, Maryland 20899, USA

\*scott.schmucker@nist.gov \*stew@nist.gov

Scanning tunneling microscopy (STM) enables the fabrication of 2-D delta-doped structures in Si with atomistic precision, with applications from tunnel field effect transistors to qubits. The combination of a very small contact area and the restrictive thermal budget necessary to maintain the integrity of the delta layer make developing a robust electrical contact method a significant challenge to realizing the potential of atomically precise devices. Here, we demonstrate a method for electrical contact using Pd<sub>2</sub>Si formed at the temperature of silicon overgrowth (250 °C), minimizing the diffusive impact on the delta layer. We use the transfer length method to show our Pd<sub>2</sub>Si contacts have very high yield (99.7 % +0.2 % -1.5 %) and low-resistivity (272±41  $\Omega$  µm) in contacting mesa-etched Si:P delta layers. We also present three terminal measurements of low contact resistance (<1 k $\Omega$ ) to devices written by STM hydrogen depassivation lithography with similarly high yield (100 % +0 % -3.2 %).

#### I. INTRODUCTION

Fabrication of delta-doped Si:P nanostructures with atomistic precision is the subject of intense ongoing study due to the potential to utilize this system in high performance electronics and quantum computation [1–4]. While Si:P devices have been demonstrated in the laboratory, fabrication challenges intrinsic to this material make it difficult to have the yield necessary to truly exploit the system. For instance, atomically precise devices present both an extremely small contact area ( $\approx 1$  nm thick) and an extremely restrictive thermal budget (ideally  $\leq 250$  °C) to minimize dopant diffusion and retain the precision nature of the device. In Si:P quantum devices, even dopant diffusion at the atomic scale can substantially alter device operation and performance [5]. The atomically-thin structure of Si:P differentiates this material from traditional doped Si, introducing contact challenges similar to those in other 2-D systems [6]. Additionally, the Si:P device layer is buried beneath 30 nm of undoped Si, further complicating contact strategies. These issues underlie the prominent challenge in forming low-resistance, ohmic contacts with high yield, and require a reexamination of contact technology.

Several electrical contact techniques are currently in use. An Al 'spiking' approach, in which metal pads are deposited and annealed at  $\approx$ 350 °C [4], produces a random distribution of Al spikes between the Si/Al interface and the delta-doped structure. This process can be unreliable for micrometer scale contact pads: no spikes may form or the penetration depth may be too shallow. To overcome the randomness of Al spiking, lithographically defined vias can be filled with Al metal [7], forming edge contacts to the delta layer. Using vias to form reliable contacts requires a clean interface at the  $\approx 1$  nm thick delta layer edge, while also finely tuning the etch process to ensure a bowl-shaped geometry to maximize contact area. These considerations lead to a precariously narrow process window for viaetched contacts. In one case, vias are reported to provide contact resistances  $<100 \text{ k}\Omega$ . [8] Another approach is the formation of preimplanted contacts which are then relocated in

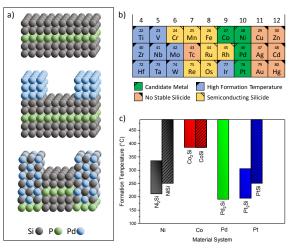

FIG 1. Silicide contact process and selection of transition metal. (a) Si:P device is buried beneath 30 nm of epitaxial Si. Pd metal pads are deposited in contact region and Si and Pd interdiffuse to form  $Pd_2Si$ , consuming Si and interfacing with the Si:P device. (b) Candidate metals for silicide formation (green) are identified, excluding elements which do not form stable silicides (orange), which form semiconducting silicides (yellow), and which form silicides are compared by the phases in which they exist and the temperature ranges in which these phases form. Dimetal silicide phases are shown in solid color. Monosilicides are shown with cross hatching.

situ so that device contacts are written to overlap with the pre-implanted surface [9,10]. While this approach has met with success, it restricts the thermal budget for UHV processing and gives a high parasitic resistance compared to metal contacts of the same dimensions. Pre-implanted contact resistances have been reported ranging as high as 48 k $\Omega$  [9] with the lowest published contact resistivity being  $\approx 1 \ k\Omega \ \mu m$ , a value approximated from a two-point resistance measurement. [10] The Pd<sub>2</sub>Si contacts reported here offer order of magnitude improvement over typical contact resistances and a substantial improvement in contact variability.

We address these challenges by utilizing palladium silicide (Pd<sub>2</sub>Si) to contact delta-doped Si:P devices. Pd<sub>2</sub>Si is a low-temperature metallic silicide with a hexagonal structure. As shown in Figure 1(a), the Si:P device is buried beneath a Si encapsulation layer. In our process, palladium is deposited in the contact region and annealed at 250 °C for 20 min. During annealing the Si and metal interdiffuse, consuming Si, displacing P into the substrate [11], and adjoining the Si:P device and Pd<sub>2</sub>Si contact. Pd<sub>2</sub>Si contacts form without etching, enabling a clean interface to the Si:P layer. Furthermore, the process is deterministic, with sub-surface metal diffusion occurring uniformly across each lithographically-defined contact. Thus, Pd<sub>2</sub>Si contacts combine the advantages of the common Al contacting methods discussed above while avoiding their disadvantages.

Low-temperature silicide (see Fig. 1b) contacts to conventional semiconductor devices are common practice [12], but their use for contacting 2-D Si:P delta-doped devices has been limited. Polley et al. demonstrated NiSi contacts [13,14] to eliminate complications from the

superconducting transition that occurs in Al near 1.2 K. In that work, to avoid the resistive  $Ni_2Si$  phase, samples were annealed at 400 °C, and additional etch steps were performed to remove unreacted, magnetic Ni atoms which can induce hysteretic effects in the magnetotransport. As mentioned above, our use of Pd<sub>2</sub>Si allows contacts to form at much lower temperatures and avoids magnetic materials while maintaining a straightforward process.

Finally, our choice of  $Pd_2Si$  is advantageous due to reaction kinetics. First, the choice of dimetal silicides (M<sub>2</sub>Si) is often preferable, since the metal atom tends to be the dominant diffusive species (DDS), whereas Si tends to be the DDS in monosilicides (MSi) [15]. When the metal is the DDS, formation of voids at the silicon-silicide interface is minimized and contaminants are left at the metal-silicide interface, forming a pristine interface layer abutting the Si:P layer. In contrast, when the DDS is Si, Kirkendall voids can form at the silicon-silicide interface [16]. Platinum silicide, a metallurgically-similar candidate silicide of broad interest [17,18], forms both dimetal and monosilicide phases at low-temperature [19]. In contrast, the large difference between the formation temperatures of Pd<sub>2</sub>Si (250 °C) and PdSi (820 °C) [20,21] ensures a well-controlled reaction where Pd will remain the DDS. Second, Pd can diffuse through a SiO<sub>2</sub> film more easily than Pt or Ni, meaning a thin native oxide poses less of a barrier to silicide formation [22].

$Pd_2Si$  offers the lowest formation temperature of all candidate silicides (Figure 1(c)) [14,23], reported to be from 100 °C [24,25] to 190 °C [23]. Additionally,  $Pd_2Si$  exhibits a very weak electron-phonon interaction, suggesting that any superconductivity could be easily suppressed [26]. Finally, both  $Pd_2Si$  and residual Pd metal are non-magnetic, minimizing the influence of stray magnetic moments and eliminating the need to remove residual metal.

#### II. EXPERIMENTAL PROCEDURES

Delta-doped Si:P devices are fabricated by gas-phase PH<sub>3</sub> dosing of the Si(100) surface which has been pre-patterned with etched alignment marks [27]. The 2×1 surface reconstruction is prepared by flashing to 1200 °C, cooling rapidly to 800 °C, and then cooling slowly (2.5 °C/s) to 350 °C. The surface is optionally passivated by atomic H cracked on a 1300 °C W filament (10 min) before cooling slowly to room temperature. For passivated surfaces, the device geometry is defined by hydrogen depassivation lithography [28,29] in the scanning tunneling microscope (STM) [30]. STM is performed in an Omicron VT STM with polycrystalline W tips prepared by electrochemical etching and optionally sputter sharpened [31]. The tip is biased relative to a grounded sample. For unpassivated surfaces, ~30 mm<sup>2</sup>, uniform delta-doped Si:P films ("blanket delta layers") are produced and later patterned by optical or e-beam lithography and etching after Si encapsulation. For H-passivated surfaces, the H serves as a chemical resist which is locally desorbed to expose Si dangling bonds; only the patterned area is converted to delta-doped Si:P. The surface is exposed to PH<sub>3</sub> gas at  $4 \times 10^{-6}$  Pa for 6 min, saturating unpassivated portions of the surface.

P adatoms are incorporated by annealing [32]. A 30 nm Si encapsulation layer is deposited using a SUSI Si sublimation source at a rate of 0.6 monolayers/min [33–36]. After encapsulation, the

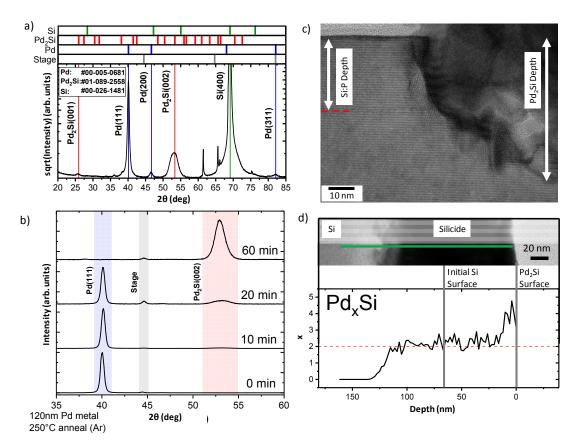

FIG 2. Analysis of the structure and formation of Pd<sub>2</sub>Si. (a) XRD spectrum of Pd film on Si(100) after partial annealing at 250 °C. Anticipated derived characteristic peaks corresponding to the Pd(111) and Si(400) peaks are indicated with arrows. (b) Progression of normalized spectra for different annealing times. The Pd(111) peak vanishes and is replaced by the Pd<sub>2</sub>Si(002) peak when annealed. (c) TEM micrograph of annealed Pd<sub>2</sub>Si contact to a Si:P delta layer (location of delta layer is indicated with a red dashed line). (d) EDS mapping across a Pd<sub>2</sub>Si contact pad at position indicated by a solid green line. The composition (Pd<sub>2</sub>Si) is uniform with the exception of a 20 nm Pd-rich ( $\approx$ Pd<sub>4</sub>Si) surface layer. The position of the original Si surface is estimated.[32]

P device has been enclosed beneath this Si layer, which allows the sample to be removed from vacuum without contaminating the active area or degrading the quality of the device. Because of this, the STM patterned devices are compatible with conventional cleanroom processing, as well as *ex situ* analysis and measurement techniques. For STM-patterned devices, patterns are

relocated to within 200 nm with Kelvin probe force microscopy (KPFM) [37,38].

Contact pads are defined by a liftoff process and electron-beam evaporation of 100 nm Pd metal at a base pressure of  $\leq 4 \times 10^{-4}$  Pa and deposition rate of 0.2 nm/s. Native SiO<sub>2</sub> is removed by immersion in 100:1 buffered HF for 1 minute immediately before evaporation. Pd<sub>2</sub>Si is formed by thermal annealing to 250 °C for 20 min with a base pressure below 0.67 Pa and back-filled with Ar to atmospheric pressure with the sample held on a SiC susceptor and temperature monitored by both a pyrometer and thermocouple. The temperature setpoint is achieved in a single step with a ramp rate of 250°C/min. Ramp time is in addition to the specified annealing time. No process for residual Pd removal is performed.

During process development, Pd and Pd<sub>2</sub>Si are characterized by X-Ray Diffraction (XRD), transmission electron microscopy (TEM), and energy dispersive X-ray spectroscopy (EDS).

Electrical measurements are performed in a closed cycle cryostat with a base temperature of 3.1K. All measurements are performed in independent systems, with removal from UHV occurring only after deposition of the Si encapsulation layer.

#### III. RESULTS AND DISCUSSION

To accommodate approximately  $1\sigma$  variations in Si encapsulation layer thickness (±2 nm), Pd thickness (±10 nm), and Pd<sub>2</sub>Si/Si interface roughness (≈10 nm), we target a Pd metal thickness of 100 nm for a nominal junction depth of 70 nm [39].

We explore the progression of silicide formation by XRD of annealed metal films deposited on chemically-passivated Si(100). Spectral peaks are identified in an annealed Pd<sub>2</sub>Si film which exhibits both Pd and Pd<sub>2</sub>Si peaks (Figure 2(a)); 120 nm of Pd has been annealed for 20 min, conditions for which Pd is partially but not fully converted to Pd<sub>2</sub>Si. The peak positions for Pd, Pd<sub>2</sub>Si, and Si are indicated above the spectrum together with peaks arising from the sample stage of our XRD system. Unlabeled peaks between 60° and 67° are derived from the Si(400) peak and result from non-monochromaticity of the X-ray beam. Spectral features are identified as the Pd(111) and Pd(200) planes and the  $Pd_2Si(002)$  plane. There is no overlap in the spectral fingerprint of these materials, as the commercial Si(100) wafer is single-crystal. The Pd film is predominantly (111) textured, and Pd<sub>2</sub>Si is (001) textured. The large spectral width of the Pd<sub>2</sub>Si peak suggests that the film is polycrystalline and has a crystallite size of  $\approx 5$  nm for annealing times  $\leq 20$  min, a result consistent with earlier studies [40]. To follow the progression of silicide formation, separate and independent samples are annealed at 250 °C for intervals from 0 to 60 minutes (Figure 2(b)). We focus on the spectral region from 35° to 60° and observe the progression from Pd to Pd<sub>2</sub>Si. To elucidate this progression, spectra are normalized so that the sum of the Pd(111) and  $Pd_2Si(002)$  peak intensities is a constant. The absence of the Pd(111)peak after annealing indicates that all Pd metal has been converted after 60 minutes. After annealing 60 minutes, the measured crystallite size increases to  $\approx 8$  nm.

We expect that texturing of the Pd<sub>2</sub>Si film is less critical when contacting the 2D delta-doped Si:P layer because contact is made along the edge of the silicide, unlike conventional semiconductor devices where the contact area can extend deeply beneath the pad. Regardless of film texture, rotational misalignment between grains will result in a varying interface between Si:P and Pd<sub>2</sub>Si. Although this electronic interface is of potential future interest, only an epitaxial silicide would allow for it to be explored in detail.

To further study contact structure and composition,  $Pd_2Si$  contacts to Si:P delta layers are extracted by focused ion beam (FIB) milling and characterized by transmission electron microscopy (TEM) and energy dispersive X-ray spectroscopy (EDS). In the TEM micrograph (Figure 2(c)) we observe penetration of Pd<sub>2</sub>Si into the substrate to a depth  $\approx$ 48 nm, crossing the Si:P delta layer (the position of the delta layer is indicated by a dashed red line). This Pd<sub>2</sub>Si penetration depth is reduced from its >60 nm bulk value at the edge of the contact pad due to a local reduction in Pd metal thickness. This is primarily a result of shadowing by resist during Pd deposition and possibly some lateral encroachment of Pd during annealing. The silicide is

| W (nm) | $R_c(\Omega)$ | $R_{s}(\Omega)$ |

|--------|---------------|-----------------|

| 50     | $3207\pm550$  | $1318 \pm 44$   |

| 200    | 531 ± 136     | $1307 \pm 22$   |

| 500    | $445\pm12$    | $1305 \pm 5$    |

| 2000   | $157 \pm 13$  | $1357 \pm 20$   |

| 5000   | $107 \pm 22$  | 1376 ± 5        |

Table I. Contact resistances extracted from TLM devices and used in the generation of Figures 3(a-b). Uncertainties correspond to a  $1\sigma$  fit uncertainty.

polycrystalline with a grain size of approximately 20 nm near the contact. The high resolution of TEM micrographs also results in limited sample size; the crystallite size determined by XRD measurements provides better statistical reliability regarding average grain size when compared to TEM. Furthermore, grain sizes near the contact area may be larger than in the bulk due to the reduced film thickness in that region which causes silicide

formation to occur more rapidly.

From a one-dimensional EDS line scan across the silicide (position indicated by a solid green line and data plotted in Figure 2(d)) we confirm that the contact is composed of  $Pd_2Si$ ,

with uniform composition throughout the bulk of the film. A Pd-rich (Pd<sub>x</sub>Si; x $\approx$ 4) surface layer  $\approx$ 20 nm in thickness is observed, which indicates incomplete silicide formation at the surface. Conductivity in the Pd<sub>2</sub>Si film is assessed with a silicide Hall bar, from which a resistivity of 80  $\mu\Omega$  cm at  $\approx$ 3K is measured, assuming the nominal depth discussed above.

To assess yield and variations in contact resistance, electrical tests are performed on blanket delta layer devices, avoiding the inherently serial process of STM lithography for which write times can be several hours depending on the device size and required precision [41].

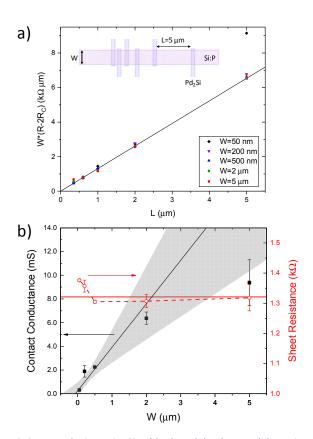

The Si:P delta layer is patterned into a Hall bar from which sheet resistance (1.3 k $\Omega$ ), carrier density (1.1×10<sup>14</sup> cm<sup>-2</sup>), and mobility (42 cm<sup>2</sup>/Vs) are extracted. These properties are a function of the specific process utilized here and can be controlled by varying process conditions. We also pattern a series of five transfer length measurement (TLM) devices of different widths (50 nm  $\leq$  W  $\leq$  5  $\mu$ m) from which contact resistance and sheet resistance are extracted. Within each TLM, channel length (L) is varied from 350 nm to 5  $\mu$ m. For each device we measure the relationship between L and the two-point resistance between consecutive contacts (R<sub>T</sub>). In this structure R<sub>T</sub> is related to contact resistance (R<sub>C</sub>) and sheet resistance (R<sub>S</sub>) by:

$$R_T = \frac{R_S}{W}L + 2R_C \tag{1}$$

For each device, a linear fit is performed and the contact resistance is extracted from the extrapolated y-intercept. Sheet resistance is extracted from the slope of the linear fit. Two outlying

points are excluded from fitting: (W=200 nm / L=350 nm) and (W=50 nm / L=5  $\mu$ m) [42]. Contact resistances and sheet resistances are shown in Table I. In Figure 3(a) we plot W×(R<sub>T</sub>-2R<sub>C</sub>) for each device, where R<sub>C</sub> is extracted from the linear fit. The collapse of all datasets to a single line indicates quality of fit, uniformity of sheet resistance, and appropriate extraction of contact resistance. A representative device geometry is shown in the inset.

FIG 3. TLM devices in Si:P blanket delta layers. (a) Device measurements in five devices with varying contact dimensions (W). Contact resistance and sheet resistance are extracted from linear fits (shown in Table I) and  $W\times(R-2R_c)$  is plotted verus L. All data collapse to a single line, shown as a guide to the eye. The geometry of the device is shown in inset. (b) Contact conductance and sheet resistance as a function of W. Sheet resistence is shown relative to value extracted from nearby Hall bar (solid red line). Contact conductance, indicated by a solid black line. 95 % confidence bands for the linear fit are shown in grey. Uncertainty in the data points corresponds to a 1 $\sigma$  fit uncertainty only.

In Figure 3(b), we plot contact conductance (solid black squares) and sheet resistance (open red circles) as a function of W. Sheet resistance extracted from the 10 µm wide Hall bar is indicated by a red line for comparison. There exists strong agreement between sheet resistances extracted from these two techniques, with deviations occurring only for small values of W (<500 nm). This deviation likely results from edge effects arising as the width of the mesa etched wire becomes small, but we cannot rule out local variations in carrier density or mobility within the delta layer at these scales. Measured contact conductance is represented by a weighted linear fit (solid black line) with  $1/\sigma^2$  weighting and 95 % pointwise confidence bands (grey) corresponding to a contact resistivity of  $\rho_c = 272\pm41 \ \Omega \ \mu m \ (R^2=0.94)$ . Here, the uncertainty reflects a  $1\sigma$  statistical fit uncertainty. We note that contact conductance appears to depart from linearity for large values

of W, but this deviation corresponds to a single data point (W = 5  $\mu$ m) with relatively large uncertainty. As typical devices include contact lengths of <2  $\mu$ m, the technologically relevant regime is low-W, where linearity is observed and the confidence band is tight.

Through the fabrication of numerous devices for a range of experimental purposes,  $313 \text{ Pd}_2\text{Si}$  contacts were formed to blanket delta layer devices, and 312 of these contacts were ohmic

and exhibited contact resistances  $\leq 1 \text{ k}\Omega$ . Unlike TLM devices, many of these contact resistances were deduced from simple two-terminal measurements and, therefore, represent upper bounds on contact resistance. This corresponds to a yield of 99.7 % +0.2 % -1.5 % with a 95 % Wilson confidence interval [43] for blanket delta layer device contacts. The minimum carrier density for tested devices was  $8 \times 10^{12} \text{ cm}^{-2}$ , which was achieved by reducing the dose of PH<sub>3</sub> gas during fabrication. All contacts were functional at this carrier density.

These results clearly demonstrate that  $Pd_2Si$  contacts to Si:P films are of low resistance and high yield. While this blanket delta layer system provides a close approximation of the STM-patterned materials which will ultimately form the basis of Si:P devices, we must demonstrate that the process is easily transferable to STM-patterned devices. One important difference

between the two systems is the presence of a mesa edge in blanket delta layer devices over which contact metal extends. STMpatterned devices eliminate this edge, thus eliminating any possibility that edge contacts might be formed.

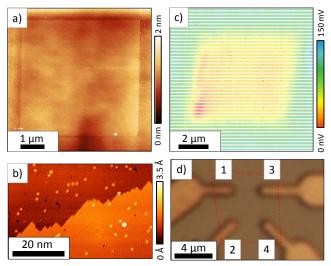

We demonstrate ohmic and low-resistance contacts to an STM-patterned  $5 \times 5 \mu m$ square van der Pauw (VdP) structure, an easily fabricated test structure used for process development and characterization. Figure 4(a) shows an STM topographic

image (-3 V, 200 pA) of the device prior to  $PH_3$  dosing. The darker regions surrounding the box correspond to the Si(100) 2×1:H surface. The bright box in the center of the image corresponds to chemically-reactive Si dangling bonds which have been exposed by electron-stimulated desorption of a H passivation

FIG 4. Contacts to STM-patterned device. (a) STM topograph of device prior to  $PH_3$  dosing. (b) STM topograph of Si(100) 2×1:H surface prior to lithographic patterning. Bright spots correspond to isolated Si dangling bonds. Isolated bonds will not facilitate spurious P atom incorporation. (c) KFPM image of surface potential after overgrowth, indicating location of device and allowing alignment of contact pads relative to etched alignment marks. (d) Optical image of device after fabrication of contacts. Device location is indicated by dashed red box. Contacts are identified by number.

layer in the STM. Figure 4(b) shows an atomic-scale STM topographic image (-3 V, 200 pA) of the same area prior to H depassivation lithography. A typical Si(100) 2×1:H surface is seen with dimer row resolution and terracing. Bright spots represent single Si dangling bonds; note that a single dangling bond is not sufficient to induce the incorporation of a spurious P atom, a cluster of  $\approx 6$  dangling bonds is necessary for this to occur [2]. Lithography was performed with a tip bias of -10 V, tunneling current of 200 nA, and dose of 10  $\mu$ C/ $\mu$ m<sup>2</sup>. After Si overgrowth to a nominal depth of 30 nm, the device is relocated by KPFM (Figure 4(b)) relative to etched alignment marks. Contact pads are defined by e-beam lithography, shown in Figure 4(c) with a red dashed line approximating the outline of the device, which is not visible by optical microscopy. From the VdP device, a carrier density of 8.0×10<sup>13</sup> cm<sup>-2</sup> and mobility of 44 cm<sup>2</sup>/Vs are measured.

The VdP device is utilized as a Kelvin contact resistance test structure to estimate contact resistance [44]. Although the VdP geometry is not ideally suited for this measurement, upper bounds for contact resistance can be extracted. The resulting contact resistances are:  $\leq$ 775  $\Omega$  (Contact 1),  $\leq$  952  $\Omega$  (Contact 2),  $\leq$ 709  $\Omega$  (Contact 3), and  $\leq$ 729  $\Omega$  (Contact 4). The actual contact resistances are likely lower than these conservative estimates. Contact resistances in this device may be higher than in the blanket delta layer due to lower carrier density in this STM-patterned VdP (27 % lower compared to blanket delta layer devices). In total, 117 Pd<sub>2</sub>Si contacts to functional STM-patterned devices have been tested, all of which were found to provide ohmic electrical contact with estimated contact resistances <1 k $\Omega$ . Non-functional devices were excluded from consideration, but only if they could be independently verified to be defective for

reasons unrelated to contacts using TEM, atomic force microscopy, or optical microscopy. From these measurements, the contact yield for STM-patterned devices is 100 % + 0 % - 3.2 % with a 95 % Wilson confidence interval [43].

#### **IV. CONCLUSIONS**

In this work, we demonstrate a novel contact scheme for delta-doped Si:P quantum devices using Pd<sub>2</sub>Si with noteworthy resistivity and yield. The simplicity of this approach makes it readily applicable to Si:P device technologies. The low contact resistivity exhibited by Pd<sub>2</sub>Si will allow for reduced write times and overhead associated with STM-defined contact pads. The high yield will enable reliable contacts to complex device architectures such as multiple-qubit systems.

Pd<sub>2</sub>Si contacts are stoichiometrically uniform, conductive at low temperature (80  $\mu\Omega$  cm at  $\approx$ 3K), and compatible with devices formed either by etching blanket delta layers or by STM-based patterning of Si(100) 2×1:H. Moreover, Pd<sub>2</sub>Si contacts are compatible with a range of device layer carrier densities ranging from 8.0×10<sup>12</sup> cm<sup>-2</sup> to 1.1×10<sup>14</sup> cm<sup>-2</sup>. As Si:P carrier densities fall, the width of the Schottky barrier increases, moving contacts out of the tunneling regime. The larger the range of carrier densities for which ohmic contact can be made, the greater the scope of devices and physics which can be investigated. Further study is required to explore the limits of Pd<sub>2</sub>Si contacts to lightly doped Si:P films, but it is noteworthy that the reduction in carrier density seen here does not substantially increase contact resistance.

The resulting contact resistivity is low:  $272\pm41 \ \Omega \ \mu m$  for blanket delta layers with carrier densities of  $1.1 \times 10^{14} \text{ cm}^{-2}$ . These results indicate that a 1 k $\Omega$  contact resistance is achievable for 300 nm contacts, a size consistent with typical Si:P contact geometries. For STM-patterned devices with lower carrier densities of  $8.0 \times 10^{13} \text{ cm}^{-2}$ , contact resistances below 1 k $\Omega$  are measured with contact lengths of order 1  $\mu m$ . This low contact resistance will allow for STM-patterned contact pads to be made smaller, reducing STM write times and contact pad footprints, allowing additional surface area to be dedicated to the active portions of devices.

In the case of Si:P blanket delta layers, we demonstrate a yield of 99.7 % +0.2 % -1.5 % with 95 % confidence. For STM-patterned devices, we demonstrate a yield of 100 % +0 % -3.2 % with 95 % confidence. With a yield >96.8 %, the expected number of functional contacts fabricated before failure is >31 for STM-patterned devices. This suggests that a 5-qubit device (3 contacts per qubit) could be made with yield >60 % due to contacts alone. As all STM-fabricated device contacts in this work were functional, this yield estimate may rise with additional testing.

In addition to implications in the field of Si:P quantum device fabrication, it is expected that Pd<sub>2</sub>Si contacts will offer enduring advantages as the development of delta-doped materials continues beyond Si:P. While Si:P provides a well-understood material testbed for contact development, this work additionally suggests the potential for silicide contacts to other material systems, including delta-doped Si:B or Si:Al [45], for which fabrication technologies remain in developmental stages. Achieving reliable electrical contacts for these systems could accelerate development of this burgeoning class of bipolar quantum materials.

The fabrication technology presented here enables the formation of reliable, low-resistance electrical contacts to buried Si:P quantum devices for a wide range of carrier densities.  $Pd_2Si$  contact technology consistently provides ohmic contacts with high yield, reducing one persistent barrier to the advancement of Si quantum device fabrication to a technologically relevant scale.

#### ACKNOWLEDGEMENTS

This work was supported by the Atom-Based Devices Innovations in Measurement Science (IMS) project at NIST. This work was performed in part at the Center for Nanoscale Science and Technology (CNST) at NIST. The authors acknowledge helpful discussions with Gerard Henein, Josh Pomeroy, Curt Richter, Kerry Siebein, and Neil Zimmerman. Certain commercial equipment, instruments, or materials are identified in this paper to foster understanding. Such identification does not imply recommendation or endorsement by the National Institute of Standards and Technology, nor does it imply that the materials or equipment identified are necessarily the best available for the purpose.

#### References

- [1] M. Y. Simmons, F. J. Rueß, K. E. J. Goh, T. Hallam, S. R. Schofield, L. Oberbeck, N. J. Curson, A. R. Hamilton, M. J. Butcher, R. G. Clark, and T. C. G. Reusch, Scanning probe microscopy for silicon device fabrication, Mol. Simulat. **31**, 505 (2005).

- [2] M. Fuechsle, J. A. Miwa, S. Mahapatra, H. Ryu, S. Lee, O. Warschkow, L. C. L. Hollenberg, G. Klimeck, and M. Y. Simmons, A single-atom transistor, Nat. Nano. 7, 242 (2012).

- [3] F. A. Zwanenburg, A. S. Dzurak, A. Morello, M. Y. Simmons, L. C. L. Hollenberg, G. Klimeck, S. Rogge, S. N. Coppersmith, and M. A. Eriksson, Silicon quantum electronics, Rev. Mod. Phys. 85, 961 (2013)

- [4] F. J. Rueß, L. Oberbeck, M. Y. Simmons, K. E. J. Goh, A. R. Hamilton, T. Hallam, S. R. Schofield, N. J. Curson, and R. G. Clark, Toward Atomic-Scale Device Fabrication in Silicon Using Scanning Probe Microscopy, Nano Lett. 4, 1969 (2004).

- [5] B. Koiller, X. Hu, and S. Das Sarma, Exchange in Silicon-Based Quantum Computing Architecture, Phys. Rev. Lett. **88**, 027903 (2001).

- [6] L. Wang, I. Meric, P. Y. Huang, Q. Gao, Y. Gao, H. Tran, T. Taniguchi, K. Watanabe, L. M. Campos, D. A. Muller, J. Guo, P. Kim, J. Hone, K. L. Shepard, and C. R. Dean, One-dimensional electrical contact to a two-dimensional material, Science 342, 614 (2013).

- [7] M.M Fuechsle, Ph.D. Dissertation, Precision Few-Electron Silicon Quantum Dots, University of New South Wales (2011).

- [8] S. Hile, Ph.D. Dissertation, Spin Control and Coherence in Scalable Phosphorus Donor Qubits, University of New South Wales (2017).

- [9] A. N. Ramanayaka, H.-S. Kim, K. Tang, X. Wang, R. M. Silver, M. D. Stewart, and J. M. Pomeroy, STM patterned nanowire measurements using photolithographically defined implants in Si(100), Sci. Rep. 8, 1790 (2018).

- [10] D. R. Ward, M. T. Marshall, D. M. Campbell, T. M. Lu, J. C. Koepke, D. A. Scrymgeour, E. Bussmann, and S. Misra, All-optical lithography process for contacting nanometer precision donor devices, Appl. Phys. Lett. **111**, 193101 (2017).

- [11] A. Kikuchi, Pile up of implanted phosphorus during palladium silicide formation and the characteristics of Schottky barrier diodes, J. Appl. Phys. **54**, 3998 (1983).

- [12] S.-L. Zhang and M. Östling, Metal Silicides in CMOS Technology: Past, Present, and Future Trends, Crit. Rev. Solid State **28**, 1 (2003).

- [13] C. M. Polley, W. R. Clarke, and M. Y. Simmons, Comparison of nickel silicide and aluminum ohmic contact metallizations for low-temperature quantum transport measurements, Nanoscale Res. Lett. 6, 538 (2011).

- [14] C. Polley, Ph.D. Dissertation, Four Probe, In Situ Electrical Characterization of Dopant Structures in Silicon, The University of New South Wales (2012).

- [15] L. J. Chen, Metal Silicides: An Integral Part of Microelectronics, JOM-J. Min. Met. Mat. S. 57, 24 (2005).

- [16] K. N. Tu and U. Gösele, Hollow nanostructures based on the Kirkendall effect, Appl. Phys. Lett. 86, 093111 (2005).

- [17] M. Mongillo, P. Spathis, G. Katsaros, S. De Franceschi, P. Gentile, R. Rurali, and X. Cartoixà, PtSi Clustering in Silicon Probed by Transport Spectroscopy, Phys. Rev. X 3, 041025 (2013).

- [18] T. I. Baturina, D. W. Horsell, D. R. Islamov, I. V. Drebushchak, Y. A. Tsaplin, A. A. Babenko, Z. D. Kvon, A. K. Savchenko, and A. E. Plotnikov, Josephson junction arrays on the basis of superconducting PtSi films, Physica B 329–333, 1496 (2003).

- [19] A. K. Pant, S. P. Murarka, C. Shepard, and W. Lanford, Kinetics of platinum silicide formation during rapid thermal processing, J. Appl. Phys. **72**, 1833 (1992).

- [20] H. C. Baxi and T. B. Massalski, The pdsi (palladiumsilicon) system, J. Phase Equilib. 12, 349 (1991).

- [21] J. F. Chen and L. J. Chen, Transmission electron microscopy and X-ray diffraction investigation of phase formation and transition between Pd2Si and PdSi in Pd thin films on (111)Si, Mater. Chem. Phys. **39**, 229 (1995).

- [22] D. M. Scott, S. S. Lau, R. L. Pfeffer, R. A. Lux, J. Mikkelson, L. Wieluński, and M.-A. Nicolet, The Effects of Interfacial SiO2 on Pd2Si Formation, Thin Solid Films 104, 227 (1983).

- [23] C.-D. Lien, M.-A. Nicolet, and S. S. Lau, Kinetics of Silicides on Si(100) and Evaporated Silicon Substrates, Thin Solid Films **143**, 63 (1986).

- [24] G. Ottaviani, Review of binary alloy formation by thin film interactions, J. Vac. Sci. Technol. **16**, 1112 (1979).

- [25] K. N. Tu, Selective growth of metal-rich silicide of near-noble metals, Appl. Phys. Lett. 27, 221 (1975).

- [26] P. B. Allen and W. W. Schulz, Bloch-Boltzmann analysis of electrical transport in intermetallic compounds: ReO3, BaPbO3, CoSi2, and Pd2Si, Phys. Rev. B **47**, 14434 (1993).

- [27] K. Li, N. Pradeep, S. Chikkamaranahalli, G. Stan, R. Attota, J. Fu, and R. Silver, Controlled formation of atomic step morphology on micropatterned Si(100), J. Vac. Sci. Technol. B 29, 041806 (2011).

- [28] J. W. Lyding, T. C. Shen, J. S. Hubacek, J. R. Tucker, and G. C. Abeln, Nanoscale patterning and oxidation of H-passivated Si(100)-2x1 surfaces with an ultrahigh vacuum scanning tunneling microscope, Appl. Phys. Lett. **64**, 2010 (1994).

- [29] J. N. Randall, J. W. Lyding, S. Schmucker, J. R. Von Ehr, J. Ballard, R. Saini, H. Xu, and Y. Ding, Atomic precision lithography on Si, J. Vac. Sci. Technol. B **27**, 2764 (2009).

- [30] S. R. Schofield, N. J. Curson, M. Y. Simmons, F. J. Rueß, T. Hallam, L. Oberbeck, and R. G. Clark, Atomically precise placement of single dopants in Si, Phys. Rev. Lett. 91, 13 (2003).

- [31] S. W. Schmucker, N. Kumar, J. R. Abelson, S. R. Daly, G. S. Girolami, M. R. Bischof, D. L. Jaeger, R. F. Reidy, B. P. Gorman, J. Alexander, and others, Field-directed sputter sharpening for tailored probe materials and atomic-scale lithography, Nature Commun. 3, 935 (2012).

- [32] H. F. Wilson, O. Warschkow, N. A. Marks, N. J. Curson, S. R. Schofield, T. C. G. Reusch, M. W. Radny, P. V. Smith, D. R. McKenzie, and M. Y. Simmons, Thermal dissociation and desorption of PH3 on Si(001): A reinterpretation of spectroscopic data, Phys. Rev. B 74, (2006).

- [33] J. G. Keizer, S. Koelling, P. M. Koenraad, and M. Y. Simmons, Suppressing Segregation in Highly Phosphorus Doped Silicon Monolayers, ACS Nano, 9, 7080 (2015).

- [34] X. Wang, J. A. Hagmann, P. Namboodiri, J. Wyrick, K. Li, R. E. Murray, A. Myers, F. Misenkosen, M. D. Stewart, C. A. Richter, and R. M. Silver, Quantifying atom-scale dopant movement and electrical activation in Si:P monolayers, Nanoscale 10, 4488 (2018).

- [35] X. Deng, P. Namboodiri, K. Li, X. Wang, G. Stan, A. F. Myers, X. Cheng, T. Li, and R. M. Silver, Silicon epitaxy on H-terminated Si (100) surfaces at 250 C, Appl. Surf. Sci. 378, 301 (2016).

- [36] J. A. Hagmann, X. Wang, P. Namboodiri, J. Wyrick, R. Murray, M. D. Stewart, R. M. Silver, and C. A. Richter, High resolution thickness measurements of ultrathin Si:P monolayers using weak localization, Appl. Phys. Lett. **112**, 043102 (2018).

- [37] A. K. Henning, T. Hochwitz, J. Slinkman, J. Never, S. Hoffmann, P. Kaszuba, and C. Daghlian, Two-dimensional surface dopant profiling in silicon using scanning Kelvin probe microscopy, J. Appl. Phys. 77, 1888 (1995).

- [38] E. Bussmann, M. Rudolph, G. S. Subramania, S. Misra, S. M. Carr, E. Langlois, J. Dominguez, T. Pluym, M. P. Lilly, and M. S. Carroll, Scanning capacitance microscopy registration of buried atomic-precision donor devices, Nanotechnol. **26**, 085701 (2015).

- [39] S. P. Murarka, Self-aligned silicides or metals for very large scale integrated circuit applications, J. Vac. Sci. Technol. B **4**, 1325 (1986).

- [40] H. Chen, G. E. White, S. R. Stock, and P. S. Ho, An X-Ray Study of Domain Structure and Stress in Pd2Si Films at Pd-Si Interfaces, MRS Online Proc. **10**, (1981).

- [41] J. B. Ballard, T. W. Sisson, J. H. Owen, W. R. Owen, E. Fuchs, J. Alexander, J. N. Randall, and J. R. Von Ehr, Multimode hydrogen depassivation lithography: A method for optimizing atomically precise write times, J. Vac. Sci. Technol. B 31, 06FC01 (2013).

- [42] The first point has anomalously low resistance which we speculate derives from a low-resistance parallel path due to an error in lithography. SEM imaging confirmed debris which we could not confirm as conducting. The second point has anomalously high resistance which we speculate is due to variation in the width of the 50 nm structure between the contacts separated by 5  $\mu$ m. When this point is included in the fit we obtain a negative contact resistance and higher sheet resistance. When excluded, sheet resistance agrees with five independent measurements within 10%. SEM shows ~20% mesa width reduction between these contacts.

- [43] NIST/SEMATECH e-Handbook of Statistical Methods, https://www.itl.nist.gov/div898/handbook/prc/section2/prc241.htm, June 2018.

- [44] D. K. Schroder, *Semiconductor Material and Device Characterization* (John Wiley & Sons, 2006).

- [45] A. N. Ramanayaka, H.-S. Kim, J. A. Hagmann, R. E. Murray, K. Tang, F. Meisenkothen, H. R. Zhang, L. A. Bendersky, A. V. Davydov, N. M. Zimmerman, C. A. Richter, and J. M. Pomeroy, Towards superconductivity in p-type delta-doped Si/Al/Si heterostructures, AIP Advances 8, 075329 (2018).